分類: 數據轉換和信號處理

總計:

252

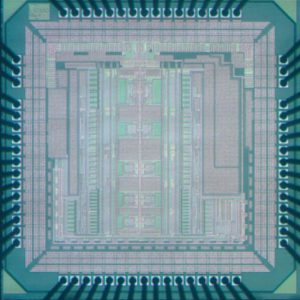

Delay Generator

Granted Number: 201246793

Application Number: 100116148

Taiwan Patent

Mar-2014

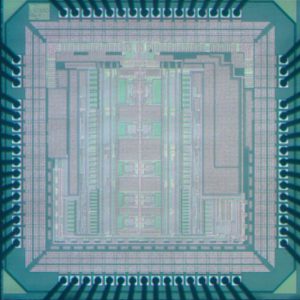

0.46mm2 4-db NF unified Receiver Front end chip

ST

65nm A 12-bit 160-Ms/s Passive Pipeline-SAR ADC Oct-2013