State-Key Laboratory of Analog and Mixed Signal VLSI, University of Macau, Macao, China, 1- also with Department of ECE, FST, University of Macau; 2- also with Synopsys Macau Ltd.;

## Research Background

### PLL based on Ring-VCO:

- Low phase noise/jitter phase-locked loops (PLLs) are critical building blocks in various systems.

- The LC oscillators have a good phase noise but suffer from large area, magnetic coupling and a small tuning range.

- Ring-VCO PLL suffers from large phase noise and requires a wide-band and high-order filtering.

#### Limitations of state-of-art PLL architectures:

- •Wide-band and high-order filtering for Ring-VCO is limited by the loop stability and reference spur.

- The proposed open loop phase noise cancellation is free from both stability and reference spur issues.

#### Key proposed techniques

- An open-loop discrete-time phase noise cancellation block.

- Domino-based sampling for good isolation

- A backend gain control algorithm

# A 430frms 2.4GHz Ring-Oscillator PLL with Backend Discrete-Time Phase Noise **Cancellation Achieving 240.5dB Jitter-FoM**

Xiaofeng Yang<sup>1</sup>, Yan Zhu<sup>1</sup>, Chi-Hang Chan<sup>1</sup>, Guan Cheng Wang<sup>1</sup>, Seng-Pan U<sup>1,2</sup>

## **Proposed Techniques**

#### **Architecture:**

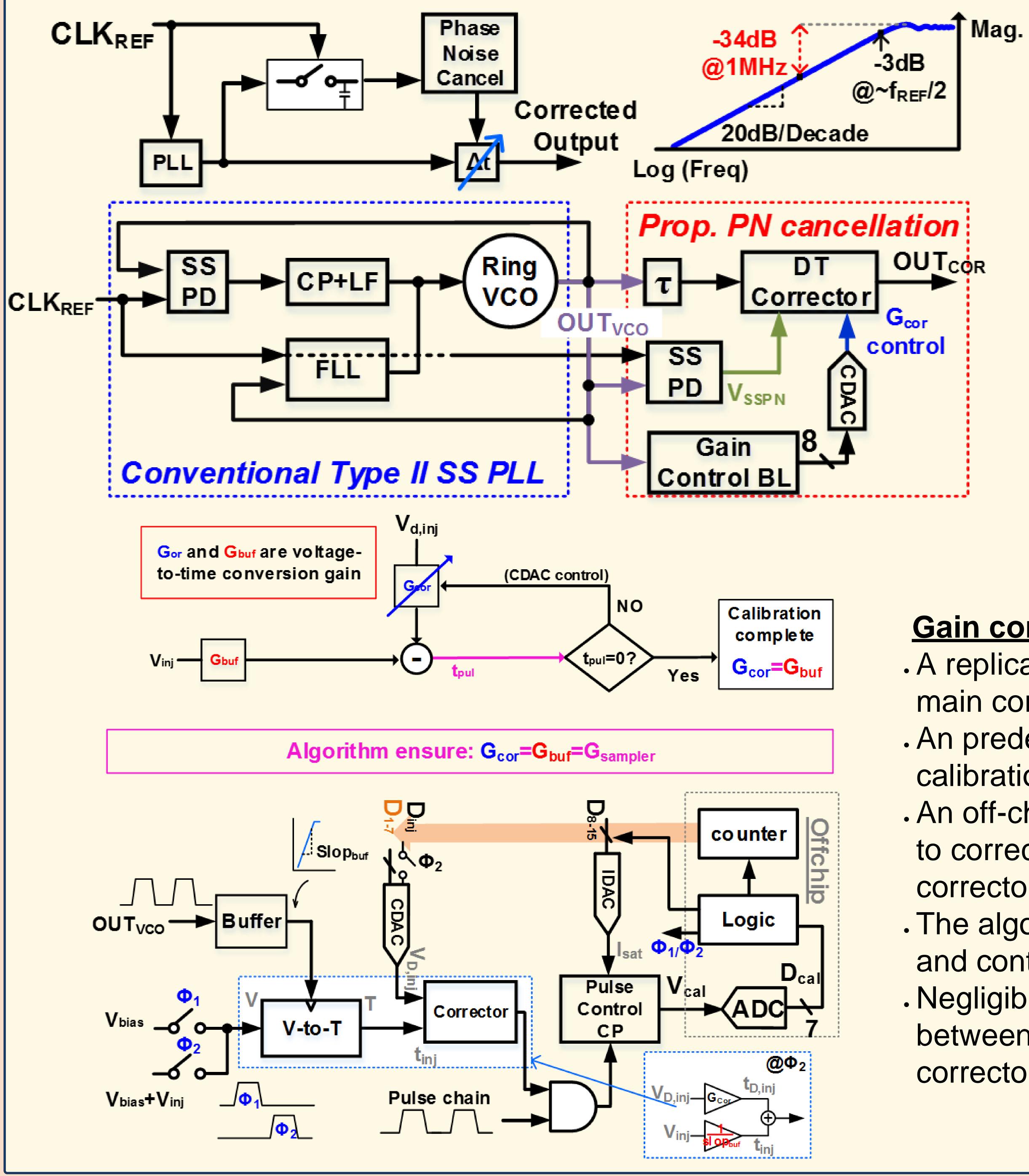

A conventional Type II sub-sampling PLL followed by a phase noise cancellation block, which provides an extra one order wide-band high-pass filtering.

#### **Open-loop phase noise** cancellation operation:

- .Sampling the noise information from the VCO's output.

- •Adjusting the timing  $\Delta t$  of a delay cell in real time.

- .Controlling the gain by CDAC.

#### **Gain control algorithm:**

- . A replica corrector with matched gain of main corrector.

- . An predefined voltages are connected to calibration circuit

- . An off-chip ADC and algorithm converging to correct bias code for CDAC of the corrector to control the corrector gain.

- . The algorithm is working in the background, and controlling the gain in real time.

- . Negligible error is caused by the mismatch between replica corrector and the main corrector.

|               | 0          |    |     |

|---------------|------------|----|-----|

| -             | -20        |    |     |

| (dBm          | -40        |    |     |

| Spectrum(dBm) | -60        |    |     |

| Spe           | -80        |    |     |

| -             | -100<br>2. | 15 | 2.2 |

|               |            |    |     |

## **Measurement Results**

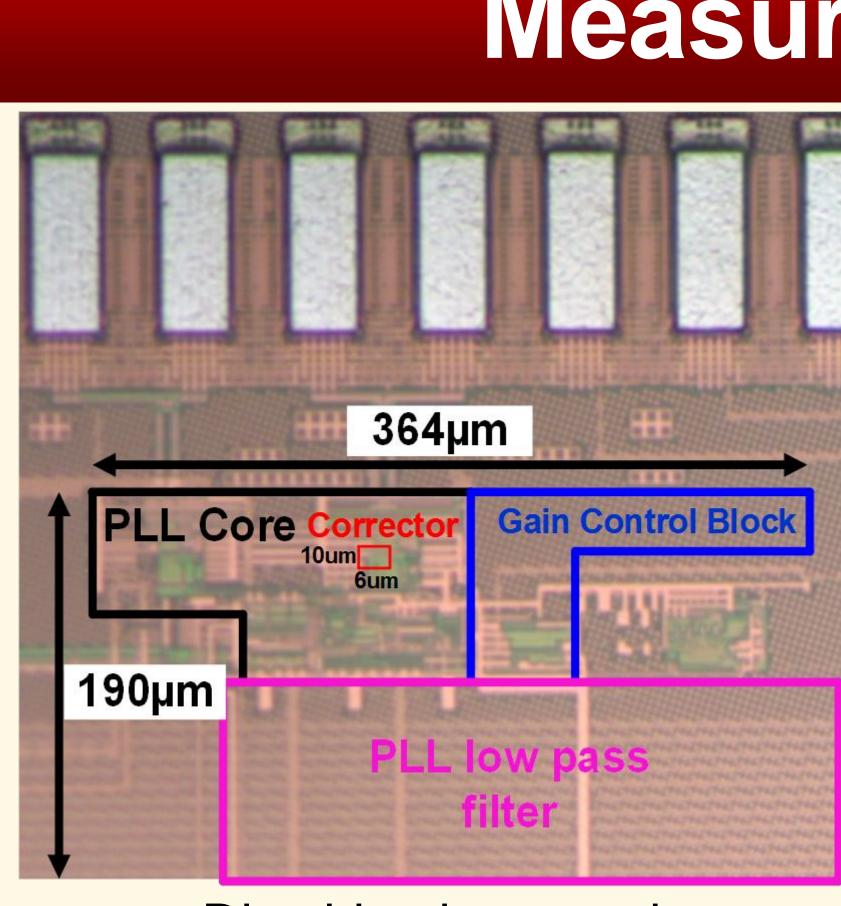

Die chip photograph

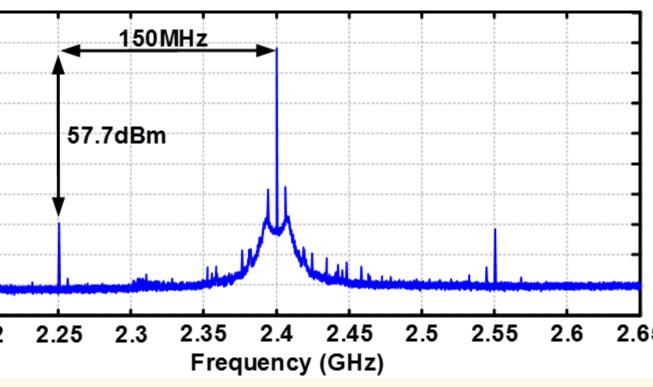

Measured reference spur

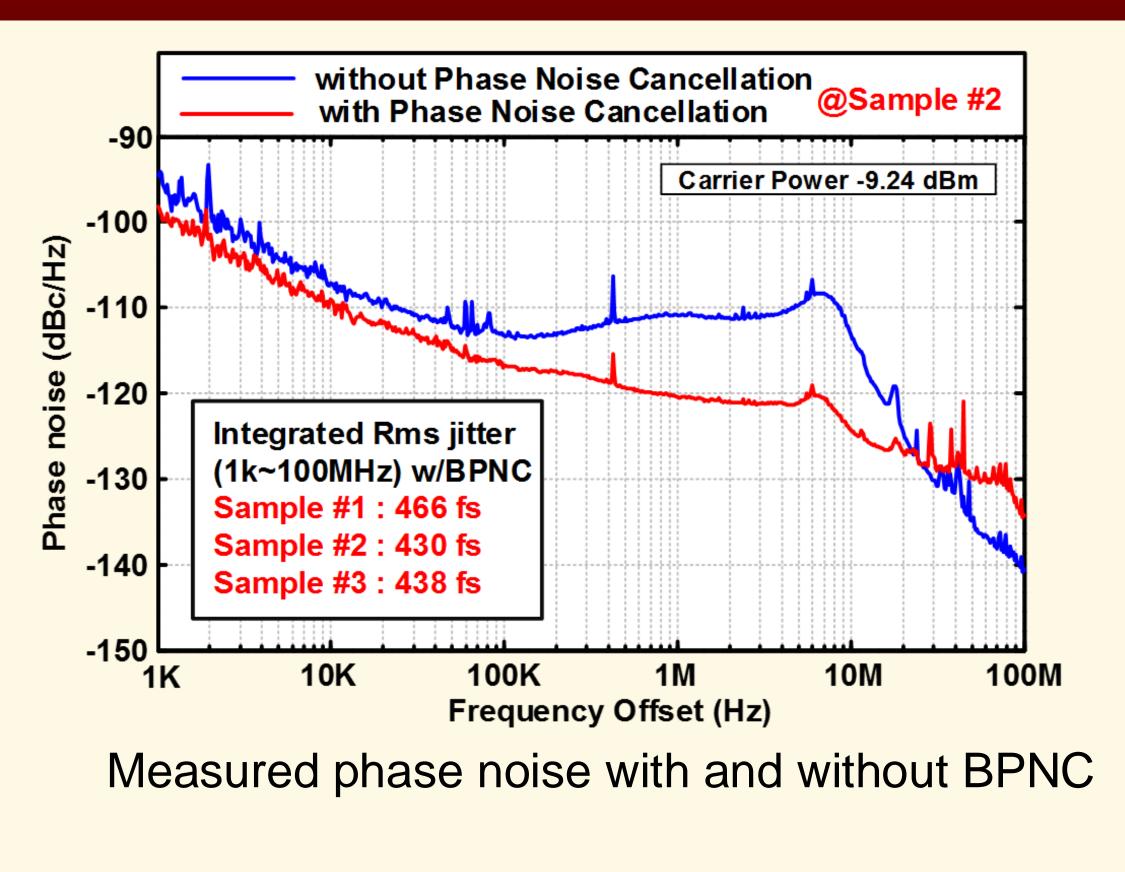

|                                    | With<br>BPNC | Without<br>BPNC |

|------------------------------------|--------------|-----------------|

| Phase noise@1MHz<br>dBc/Hz         | -120.4       | 110.9           |

| Integrated jitter<br>(1KHz~100MHz) | 430 fs       | 1.02 ps         |

## Summary and Comparison

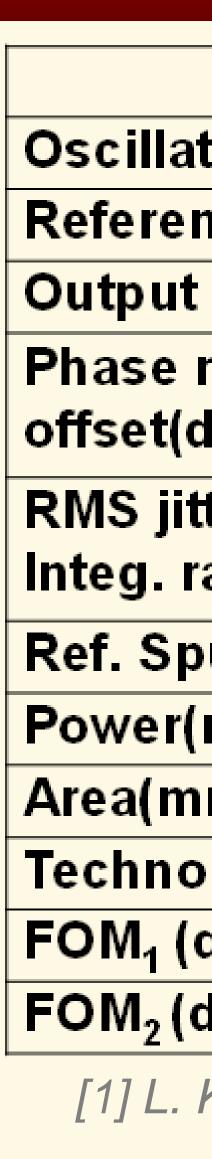

|                         | ISSCC15 [1] | ISSCC16 [2] | ISSCC17 [3] | This work   |

|-------------------------|-------------|-------------|-------------|-------------|

| ator Topology           | Ring        | Ring        | Ring        | Ring        |

| nce Freq. (MHz)         | 22.6        | 67.74       | 192         | 150         |

| t Freq. (GHz)           | 2.4         | 2.1         | 2.3         | 2.4         |

| noise @ 1MHz<br>dBc/Hz) | -113.8      | -113        | -114.4      | -120.4      |

| itter (ps)              | 0.97        | 1.05        | 0.72        | 0.43        |

| range (MHz)             | (0.001~100) | (0.001~50)  | (0.01~100)  | (0.001~100) |

| pur (dBc)               | -65         | -45         | -37         | -58         |

| (mW)                    | 4           | 3.84        | 4.59        | 4.8         |

| nm²)                    | 0.015       | 0.043       | 0.0049      | 0.056       |

| ology (nm)              | 45          | 65          | 65          | 28          |

| (dB)                    | -234.1      | -234        | -236.2      | -240.5      |

| dB)                     | 175.4       | 173.6       | 174.9       | 181.2       |

|                         |             |             |             |             |

[1] L. Kong, ISSCC2015 [2] Z. Huang,ISSCC2016 [3] J. Chuang, ISSCC2017

**★** Introduced least phase noise and no reference spur penalty. **★** The proposed architecture achieves the best both FOM1&FOM2.