## 3.9 An RF-to-BB Current-Reuse Wideband Receiver with Parallel N-Path Active/Passive Mixers and a Single-MOS Pole-Zero LPF

Fujian Lin<sup>1</sup>, Pui-In Mak<sup>1,2</sup>, Rui Martins<sup>1,2,3</sup>

<sup>1</sup>University of Macau, Macao, China, <sup>2</sup>UMTEC, Macao, China, <sup>3</sup>Instituto Superior Tecnico, Lisbon, Portugal

The latest passive-mixer-first wideband receiver (RX) [1] has managed to squeeze the power (10 to 12mW) via resonant multi-phase LO and current-reuse harmonic rejection BB, but the removals of RF gain and virtual ground severely penalize its NF (10.5±2.5dB), while devaluing its original IIP3 benefits (+10dBm). The described wideband RX exploits an RF-to-BB current-reuse topology, with parallel N-path active/passive mixers, to leverage such power-performance tradeoffs. Specifically, the RX features: 1) a current-reuse RF front-end with an N-path active mixer to realize most RF-to-BB functions in the current domain, resulting in better power efficiency and linearity; 2) a feedforward N-path passive mixer to enable LO-defined input matching with zero external components, while offering frequency-translated band-pass filtering and noise cancelling; 3) a single-MOS pole-zero LPF to perform current-mode BB filtering while alleviating the tradeoff between the in-/out-of-band linearity, and 4) a BB-only two-stage harmonic-recombination (HR) amplifier to boost the 3<sup>rd</sup> and 5<sup>th</sup> harmonic rejection ratios (HRR3,5) with low hardware intricacy. Targeting the TV-band (0.15 to 0.85GHz) cognitive radios for IEEE 802.22/802.11af, the RX manifests favorable NF (4.6±0.9dB) and out-of-band IIP2/IIP3 (+61/+17.4dBm) under low power dissipation (10.6 to 16.2mW).

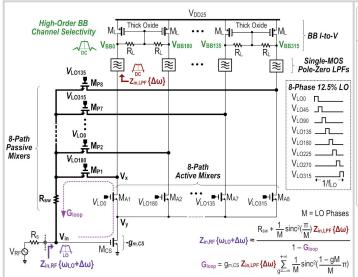

Figure 3.9.1 depicts the RF front-end that unifies most functions. A single-ended RF input  $(V_{\text{in}})$  avoids the balun and its insertion loss. The  $-g_{\text{m,CS}}$  stage  $(M_{\text{CS}})$  serves as the LNA, which is stacked by an 8-path active mixer  $(M_{\text{A1-8}})$  for down-conversion, and an 8-path current-mode LPF for channel selection before BB I-to-V conversion at R $_{\text{L}}$   $(V_{\text{BB0}},V_{\text{BB45}},\ldots V_{\text{BB315}})$ .  $M_{\text{A1-8}}$  driven by an 8-phase 12.5%-duty-cycle LO  $(V_{\text{L00}},V_{\text{L045}},\ldots V_{\text{L0315}})$  allow HR at BB to enhance the critical HRR $_{\text{2-6}}$ . A feedforward 8-path passive mixer  $(M_{\text{P1-8}})$  driven by the same set of LOs, but anti-phased with  $M_{\text{A1-8}}$ , is added for three intents:

Input Biasing: unlike the TV-band RXs in [5-6] that entail a bulky external inductor for bias and wideband impedance matching, here the gate of  $M_{\rm CS}$  is biased via the passive mixers copying the dc voltage from  $V_x$  to  $V_{\rm in}$ , avoiding any external parts while giving adequate overdrive voltage ( $V_{\rm DS}$ =420mV) on  $M_{\rm CS}$  for better linearity. Moreover, owing to no AC-coupling capacitors at  $V_{\rm in}$ , the RF bandwidth easily covers the low-frequency range.

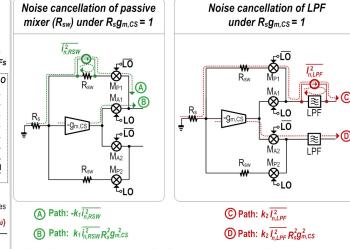

Noise Cancelling: the anti-LO-phased active and passive mixers allow concurrent noise cancellation of  $R_{sw}$  and LPF under  $g_{m,CS}R_s\!=\!1$  (Fig. 3.9.2). For the former,  $R_{sw}$  induces a noise current to  $R_s$ , and is sensed by the  $-g_{m,CS}$  stage to produce an anti-phased output nullifying the noise inherently. For the latter, when the RX is operated differentially, the LPF's noise current on  $R_s$  will be copied to another path with the same phase, being a cancellable common-mode noise. Hence, the RX NF is dominated by the thermal noise of  $M_{cS}$  (i.e., Noise Factor=1+ $\gamma$ , where  $\gamma$  is the channel noise factor), which can be upsized (W/L:120/0.18) to reduce the 1/f noise.  $M_{A1-8}$  contribute insignificant noise and are small in size (W/L:12/0.06) to save the LO power.

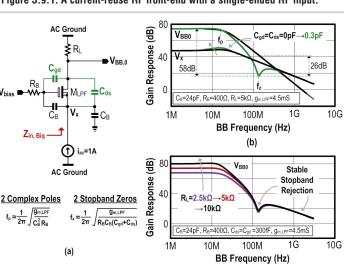

The current-mode Biguads in [5,6] only can synthesize two complex poles, while the proposed single-MOS LPF (Fig. 3.9.3) offers stronger pole-zero filtering, being more cost-effective than its real-pole-only counterparts [1-4]. The LPF's transfer function relies on  $R_B$ ,  $C_B$ , and an intentionally large transistor  $M_{LPF}$  (W/L: 768/0.5). The latter brings in large parasitics  $C_{od}$  (~0.3pF) and  $C_{ds}$  (~0.3pF) under bulk-source connection, introducing two stopband zeros. By tuning the zeros to 150MHz, stopband rejection at 100-to-200MHz offset can be enhanced, suitable for filtering the GSM850/900 bands when the RX is to operate up to 710MHz (IEEE 802.11af). The simulated bandwidth has a mean value of 14.6MHz ( $\sigma$ =0.48MHz). Another useful property of the LPF is the peaking of  $Z_{in,LPE}$  around the cutoff, which avoids the fast roll-off shape when it is translated to RF. The grounded C<sub>B</sub> essentially suppresses the out-of-band interferers before they see the active device (M<sub>LPF</sub>). Without affecting most in-band metrics, C<sub>B</sub> can be upsized to concurrently narrow the RF and BB bandwidths at the expense of die area. Elegantly, the stopband profile of this LPF is highly insensitive to R<sub>I</sub>, easing the tradeoff between the in-/out-of-band linearity. V<sub>bias</sub> from a replica RF frontend handily aids the biasing.

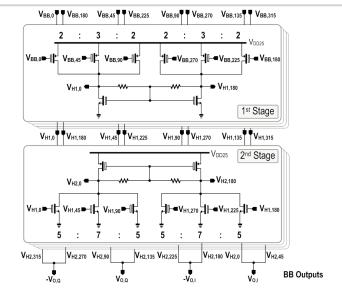

Single-stage HR shows an uncalibrated HRR $_{3.5}$  of 34 to 45dB [1,3]. The proposed BB-only two-stage HR amplifier (Fig. 3.9.4) boosts the HRR $_{3.5}$  without the gain scaling at RF [4], resulting in simpler layout and lower parasitics. Owing to the embedded BB channel selectivity at the RF front-end, the linearity of such HR amplifiers is highly relaxed, resulting in power savings. The latter also leads to limited BB bandwidth assisting the stopband rejection. The gain weighting is based on a PMOS amplifier {2:3:2} followed by an NMOS amplifier {5:7:5} to approximate the gain ratio {1: $\sqrt{2}$ :1} with <0.1% error [4]. Thus, the total relative gain error becomes insignificant due to the multiplication:  $(\epsilon_0+\epsilon_{1,HR})\epsilon_{2,HR}/4$ , where  $\epsilon_0$  is the relative gain error of the RF front-end, and  $\epsilon_{1,HR}/\epsilon_{2,HR}$  is the relative gain error of the 1s $^{1}/2$ cos stage HR amplifier. The simulated worst HRR $_{3.5}$  is >53dB (mean=62dB). Thus, the HRR $_{3.5}$  is dominated by the LO phase error.

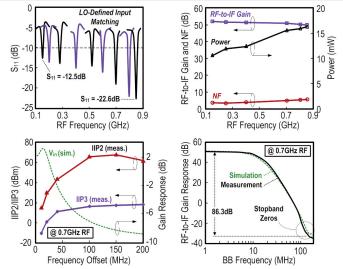

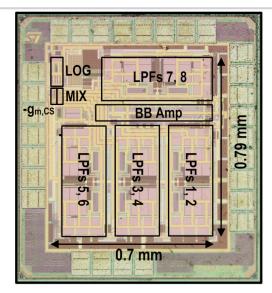

The RX fabricated in 65nm CMOS occupies a small die area of 0.55mm² that is dominated by the 8-path LPFs with  $C_{\rm B}{=}24\rm pF.$  From 0.15 to 0.85GHz, all LO-defined  $S_{11}$  are <–12.5dB. The RF-to-IF gain is  $51{\pm}1\rm dB$  and NF is  $4.6{\pm}0.9\rm dB$ . The power rises with the frequency from 10.6 to 16.2mW, in which 7.5mW due to the static power (RF+BB). At 0.7GHz RF and maximum gain, the IIP2/IIP3 raises from +15/–12dBm (in-band) to +61/+17.4dBm (out-of-band). The BB bandwidth is ~9MHz with 86.3dB stopband rejection at 150MHz offset, thanks to the dual stopband zeros. The out-of-band  $P_{1dB}$  is  $-2.5\rm dBm$  at 50MHz offset, enhanced by the RF filtering.

The chip summary is given in Fig. 3.9.6. Benchmarking with the passive-mixer-based RXs [1-4], this work succeeds in saving the power without sacrificing the NF, out-of-band linearity and HRR. No external component is entailed and stronger BB filtering is achieved in a small die size. Figure 3.9.7 shows the RX die micrograph.

## Acknowledgements:

This work was funded by the Macao FDCT and UM - MYRG114-FST13-MPI.

## References

- [1] C. Andrews, et al., "A Wideband Receiver with Resonant Multi-Phase LO and Current Reuse Harmonic Rejection Baseband," *IEEE J. Solid-State Circuits*, vol. 48, pp. 1188-1198, May 2013.

- [2] J. Borremans et al., "A 0.9V Low-Power 0.4-6GHz Linear SDR Receiver in 28nm CMOS," *Symp. on VLSI Circuits, Dig. Tech. Papers*, pp. 146-147, June 2013.

- [3] D. Murphy et al., "A Blocker-Tolerant Wideband Noise-Cancelling Receiver with a 2dB Noise Figure," *ISSCC Dig. Tech. Papers*, pp. 74-75, Feb. 2012.

- [4] Z. Ru et al., "A Software-Defined Radio Receiver Architecture Robust to Out-of-Band Interference," *ISSCC Dig. Tech. Papers*, pp. 230-231, Feb. 2009.

- [5] P.-I. Mak et al., "A 0.46mm<sup>2</sup> 4-dB NF Unified Receiver Front-End for Full-Band Mobile TV in 65nm CMOS," *ISSCC Dig. Tech. Papers*, pp. 172-173, Feb. 2011.

- [6] J. Greenberg et al., "A 40MHz-to-1GHz Fully Integrated Multistandard Silicon Tuner in 80nm CMOS," *ISSCC Dig. Tech. Papers*, pp. 162-163, Feb. 2012.

Figure 3.9.1: A current-reuse RF front-end with a single-ended RF input.

Figure 3.9.3: a) Single-MOS pole-zero LPF. b) Simulated V  $_{\rm BBO}$  and V  $_{\rm x}$  showing the rejection added by the stopband zeros. c) Sizing R  $_{\rm L}$  for In-band gain.

Figure 3.9.5: Measured  $S_{11}$ ; RF-to-IF gain, NF and power; IIP2/IIP3; RF-to-IF gain response.

$k_1$  and  $k_2$  are constant representing the noise currents leak to  $R_8$

Figure 3.9.2: Simplified two-phase noise equivalent circuits of the RF frontend showing the noise cancellation of  $R_{sw}$  (left) and LPF (right).

Figure 3.9.4: BB-only 2-stage harmonic-recombination (HR) amplifier.

|                                    | This Work                                                     | JSSC'13 [1]                      | VLSI'13 [2]                                               | ISSCC'12 [3]                                          | ISSCC'09 [4]                       |

|------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------------------------------------------|-------------------------------------------------------|------------------------------------|

| RX Architecture                    | Current-Reuse RF Front-<br>End + Feedforward<br>Passive Mixer | Passive Mixer<br>+ BB LNA        | RF LNA + Passive<br>Mixer + G <sub>m</sub> -C<br>+ Op-Amp | 2-Path Noise-<br>Cancelling+ Passive-<br>Mixer+ OpAmp | RF LNA+<br>Passive Mixer<br>Op-Amp |

| Downconversion                     | Active // Passive                                             | Passive                          | Passive                                                   | Passive                                               | Passive                            |

| RF Input Style                     | Single-Ended                                                  | Single-Ended                     | Differential                                              | Single-Ended                                          | Differential                       |

| RF Range (GHz)                     | 0.15 to 0.85                                                  | 0.7 to 1.6<br>(8-phase path)     | 0.4 to 3<br>(8-phase path)                                | 0.08 to 2.7                                           | 0.4 to 0.9                         |

| Power (mW) @ RF                    | 10.6 @ 0.15GHz<br>16.2 @ 0.85GHz                              | 10~12 @ 0.7GHz<br>10~12 @ 1.6GHz | 20 @ 0.4GHz<br>40 @ 3GHz                                  | 37 @ 0.08GHz<br>70 @ 2.7GHz                           | 49 @ 0.4GHz<br>60 @ 0.9GHz         |

| DSB NF (dB)                        | 4.6±0.9                                                       | 10.5±2.5                         | 1.8 to 2.4                                                | 1.9±0.4                                               | 4±0.5                              |

| Ultimate Out-of-Band<br>IIP3 (dBm) | +17.4                                                         | +10                              | +3                                                        | +13.5                                                 | +16                                |

| Ultimate Out-of-Band<br>IIP2 (dBm) | +61                                                           | +26.6                            | +85 (calibrated)                                          | +54                                                   | +56                                |

| External Parts                     | Zero                                                          | Zero                             | Transformer                                               | Zero                                                  | 2 Inductors an<br>1 Transforme     |

| Active Area (mm²)                  | 0.55                                                          | 2.9 (inc. VCOs)                  | ~0.5 (from Fig.)                                          | 1.2                                                   | 1                                  |

| BB Filtering Style                 | 2 Complex Poles<br>+ 2 Stopband Zeros<br>(Current-Mode)       | 1 Real Pole<br>(Passive-RC)      | 2 Real Poles<br>(Active/<br>Passive-RC)                   | 2 Real Poles<br>(Active/Passive-RC)                   | 2 Real Poles<br>(Active-RC)        |

| HRR <sub>3,5</sub> (dB)            | >53, >51                                                      | 34, 34                           | 70, 55 (calibrated)                                       | 42, 45                                                | 60, 64                             |

| BB Bandwidth (MHz)                 | 9                                                             | 20                               | 0.5 to 50                                                 | 2                                                     | 12                                 |

| RF-to-IF Gain (dB)                 | 51±1                                                          | 37                               | 36                                                        | 72                                                    | 34.4±0.2                           |

| Supply (V)                         | 1.2, 2.5                                                      | 1.3                              | 0.9                                                       | 1.3                                                   | 1.2                                |

| CMOS Technology                    | 65 nm                                                         | 65 nm                            | 28 nm                                                     | 40 nm                                                 | 65 nm                              |

Figure 3.9.6: Chip summary and benchmark with recent passive-mixer-based RXs [1-4].

## **ISSCC 2014 PAPER CONTINUATIONS**

Figure 3.9.7: RX die micrograph.