# Using EDA Tools to Push the Performance Boundaries of an Ultralow-Power IoT-VCO at 65nm

Ricardo Martins, Nuno Lourenço, Nuno Horta Instituto de Telecomunicações, Instituto Superior Técnico – Universidade de Lisboa Lisboa, Portugal ricmartins@lx.it.pt, nlourenco@lx.it.pt, nuno.horta@lx.it.pt

Abstract-Voltage-controlled oscillators (VCOs) embedded in state-of-the-art radio-frequency (RF) integrated circuit (IC) multistandard transceivers must comply with extreme ultralow power requirements for modern IoT applications. However, due to the countless tradeoffs that must be considered, their manual design hardly approaches the full potential that a certain topology can achieve at advanced integration nodes. In this paper, the design and optimization of a complex IoT-VCO for a 65 nm process design kit (PDK) is fully supported by electronic design automation (EDA) tools. Firstly, a 108-dimensional performance space is optimized, providing 48 sizing solutions where the power consumption varies from 0.145 mW to 0.329 mW on the worst-case corner performance of the worstcase tuning range. Afterwards, the layout-versus-schematic (LVS) correct layout of each solution is automatically generated using a hierarchical Placer and group-based Router. Post-layout validation is carried in all solutions, and, a promising solution with 0.348 mW of worst-case post-layout power consumption is proposed for fabrication.

## I. INTRODUCTION

VCOs are essential in modern RF ICs multi-standard transceivers, and, are subject to continuous research efforts that push the boundaries of their multifaceted performance/power efficiency in state-of-the-art applications and integration technologies [1, 2]. However, the proper analysis of the design tradeoffs is impractical, as a large amount of conflicting performance figures obtained from multiple modes, test benches and/or analysis are weighted simultaneously. Their performance inflation in the presence of process variations turns the problem to proportions beyond human capabilities, which can only be solved with the support of optimization-based tools [3-5]. Moreover, due to the severe impact of layout parasitics at gigahertz frequencies, layout-aware sizing methodologies were proposed to shorten the gap between electrical and physical design steps, by generating the complete layout during the optimization flow [6-8]. Nonetheless, as the complexity of stateof-the-art RF circuits increases, the enormous simulation and layout generation times hamper the generalized application of these EDA tools, and, are still pushing the computational capabilities of modern workstations to its limits.

In this paper, the role of EDA frameworks in the design and optimization of complex RF topologies is shown, by adapting an established tool and applying it to a VCO topology for state-ofthe-art IoT specifications at a 65 nm PDK. Firstly, the sizes of its devices are optimized in a performance space obtained from 14 time-consuming steady-state (SST)/SST noise analysis. Afterwards, the complete layout of each solution is generated

978-1-7281-1201-5/19/\$31.00 ©2019 IEEE

Jun Yin, Pui-In Mak, Rui P. Martins

State-Key Laboratory of Analog and Mixed-Signal VLSI and FST-ECE, University of Macau Macao, China junyin@umac.mo, pimak@umac.mo, rmartins@umac.mo

using instances of the parametric cells provided by the foundry, and, routed using a group-based scheme. The obtained layouts are verified and extracted in most established off-the-shelf CAD tools, and, the obtained insights on the post-layout performance space are used to re-iterate and devise a solution for fabrication. The remainder document is organized as follows. In section II, the sizing optimization of the IoT-VCO is presented. Afterwards, section III addresses the automatic layout, and, section IV, the conclusions and future research directions.

# II. SIZING OPTIMIZATION SETUP & RESULTS

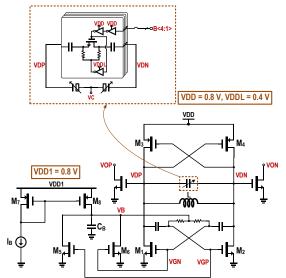

Fig. 1 introduces the schematic of the IoT-VCO [9] where the proposed method was applied. A supply voltage of 800 mV and an  $I_B$  of 10  $\mu$ A was used for a 65 nm CMOS PDK.

Fig. 1. IoT-VCO with a 4-bit binary-sized switched-capacitor array for increased tunning range.

This IoT-VCO topology aims to achieve an ultralow power while still keep good phase noise performance. To reduce the power consumption, the NMOS-PMOS complementary crosscoupled pair ( $M_1$  and  $M_2$ ,  $M_3$  and  $M_4$ ) are used in the class-C mode. To guarantee the robust start-up under different process corners, a dynamic biasing scheme is used to generate VB by  $M_5$ and  $M_6$  [10, 11]. A 4-bit binary-sized switched-capacitor array (SCA) together with A-MOS varactors are employed to tune the

This work is funded by FCT/MEC through national funds and when applicable co-funded by FEDER – PT2020 partnership agreement under the project UID/EEA/50008/2019, by the Macao Science and Technology Development Fund (FDCT) SKL Fund, and, by University of Macau (Grant MYRG2018-00220-AMSV).

VCO frequency from 4.5 to 5.4 GHz continuously [4]. The SCA biasing voltage  $V_{DDH}$  and  $V_{DDL}$  are 800 mV and 400 mV. The inductor topology adopted is an octagonal spiral inductor in ultra-thick metal and the inductor model provided by the foundry supports the change of different dimension parameters.

# A. Design Variables

The netlist of the IoT-VCO was parameterized, and, Table I details the limits and ranges of each of the 22 variables used for optimization. Note that the sizes of the *n*-type transistors and the poly resistors from the 4-bit SCA, the digital control of SCA, moscap varactor, and, output buffers, were imposed by the circuit designer and kept fixed during optimization.

TABLE I. OPTIMIZATION VARIABLES & DESCRIPTION

| Variable                                                                                             | Units | Min. | Grid | Max. |

|------------------------------------------------------------------------------------------------------|-------|------|------|------|

| radius <sup>1</sup>                                                                                  | μm    | 15   | 5    | 90   |

| turns <sup>1</sup>                                                                                   | -     | 1    | 1    | 6    |

| spacing <sup>1</sup>                                                                                 | μm    | 2    | 1    | 4    |

| width <sup>1</sup>                                                                                   | μm    | 3    | 1    | 30   |

| nccl <sup>2,7</sup> , pccl <sup>3</sup>                                                              | nm    | 60   | 20   | 240  |

| nccnf <sup>2</sup> , pccnf <sup>3</sup> , m56nf <sup>7</sup> , m78nf <sup>8</sup>                    | -     | 1    | 1    | 32   |

| nccw <sup>2</sup> , pccw <sup>3</sup> , m56w <sup>7</sup>                                            | μm    | 0.6  | 0.2  | 6    |

| m78l <sup>8</sup>                                                                                    | nm    | 130  | 20   | 6000 |

| m78w <sup>8</sup>                                                                                    | nm    | 120  | 20   | 6000 |

| rccl <sup>5</sup>                                                                                    | μm    | 0.8  | 0.2  | 30   |

| ccpnv <sup>4</sup> , ccpnh <sup>4</sup> , vbnv <sup>6</sup> , vbnh <sup>6</sup> , scanv <sup>9</sup> | -     | 6    | 2    | 100  |

| scanh <sup>9</sup>                                                                                   | -     | 6    | 2    | 50   |

<sup>1</sup>radius, turns, spacing and width are the inner radius, number of turns, spacing between conductors and conductor width of the inductor L; <sup>2</sup>nccl, nccw and nccnf are the length, width per finger and number of fingers of the cross-coupled  $M_1/M_2$ RF transistors; <sup>3</sup>pccl, pccw and pccnf are the length, width per finger and number of fingers of the cross-coupled  $M_3/M_4$ RF transistors; <sup>4</sup>ccpnv and ccpnh are the number of vertical and horizontal fingers for a width/spacing of 100 nm of the MOM capacitors from the VCO core; <sup>5</sup>rccl is the segment length for a segment width of 0.5 µm of the poly resistors from the VCO core; <sup>6</sup>vbnv and vbnh are the number of vertical and horizontal fingers for a width/spacing of 100 nm of the C<sub>B</sub> MOM capacitor; <sup>7</sup>nccl, m56w and m56nf are the length, width per finger and number of fingers of the Ms/M<sub>6</sub> RF transistors; <sup>8</sup>m78l, m78w and m78nf are the length, width per finger and number of fingers of the Ms/M<sub>8</sub> transistor (the width of M<sub>7</sub> is m78w/2); <sup>9</sup>scanv and scanh are the number of vertical and horizontal fingers for a width/spacing of 100 nm of capacitors from the SCA, using device multiplier ratio of 8:4:2:1.

## B. Test benches and Measurements

For each different tuning frequency of the SCA control, B<4:1>, a SST analysis is configured to extract the oscillation frequencies at standard supply voltage,  $f_{osc}$ , phase noises, *PN*, power consumption, and, compute the figure-of-merit, FOM:

$$FOM = -10 \log \left[ \frac{P_{dc}}{1mW} \cdot \left( \frac{\Delta \omega}{\omega_0} \right)^2 \right] - PN(\Delta \omega) \quad [dBc/Hz] \quad (1)$$

where  $\omega_0$  is the oscillation frequency,  $P_{dc}$  the power consumption,  $\Delta \omega$  is the offset from the output frequency and  $PN(\Delta \omega)$  is the oscillator phase noise. Additionally, two SST analysis are performed to extract the  $f_{osc}$  for a supply voltage of 750 mV and 850 mV, used to compute the frequency sensitivity due to a supply voltage variation, *fssv*, of 50 mV:

$$fssv = \left| \frac{f_{osc}@Vdd_2 - f_{osc}@800mV}{Vdd_2 - 800mV} \right| \quad [Hz/V]$$

(2)

where  $f_{osc} @Vdd_2$  is the oscillation frequency at the different supply voltage  $Vdd_2$ . These three test benches are designated in

Table II by SST@800<sub>bxxxx</sub>, SST@750<sub>bxxxx</sub> and SST@850<sub>bxxxx</sub>, respectively. The following process corners were considered: slow N/slow P (SS), slow N/fast P (SF), fast N/slow P (FS), and, fast N/fast P (FF). Therefore, 8 additional testbenches were added to the previous typical (TT) setup. This resulted in a 108-dimensional performance space spread through two different modes (b<sub>0000</sub> and b<sub>1111</sub>), resultant from 14 different testbenches simulated with the same 22-dimensional design variable space *x*. Note that only b<sub>1111</sub> and b<sub>0000</sub> tunings are verified since the continuous tuning between 4.5 GHz and 5.4 GHz is guaranteed by a device multiplier ratio of 8:4:2:1 on the 4-bit SCA.

TABLE II. 64 MEASURES OBTAINED FROM 14 DIFFERENT TESTBENCHES, AND, 44 EXPRESSIONS AS FUNCTIONS OF THE SIMULATIONS' OUTPUT. {CORNER} MEASURES ARE OBTAINED FOR TT, SS, SF, FS AND FF.

| Measure                                             | Units  | Measured from                 |

|-----------------------------------------------------|--------|-------------------------------|

| f <sub>osc</sub> [b <sub>0000</sub> ]@800mV{corner} | GHz    | SST@800b0000 {corner}         |

| $f_{osc}[b_{1111}] @ 800 mV \{ corner \}$           | GHz    | SST@800b1111{corner}          |

| $f_{osc}[b_{0000}] @750 mV\{TT\}$                   | GHz    | SST@750b0000{TT}              |

| $f_{osc}[b_{1111}] @750 mV\{TT\}$                   | GHz    | SST@750 <sub>b1111</sub> {TT} |

| $f_{osc}[b_{0000}] @850 mV\{TT\}$                   | GHz    | SST@850b0000{TT}              |

| $f_{osc}[b_{1111}] @850 mV\{TT\}$                   | GHz    | SST@850 <sub>b1111</sub> {TT} |

| PN[b0000]@10kHz/100kHz/1MHz/10MHz{corner}           | dBc/Hz | SST@800b0000 {corner}         |

| PN[b1111]@10kHz/100kHz/1MHz/10MHz{corner}           | dBc/Hz | SST@800b1111 {corner}         |

| power[b <sub>0000</sub> ]{corner}                   | mW     | SST@800b0000 {corner}         |

| power[b <sub>1111</sub> ]{corner}                   | mW     | SST@800b1111 {corner}         |

| Expressions                                         | Units  | <b>Computed from</b>          |

| fssv[b0000]@750mV/850mV{TT}                         | MHz/V  | Equation (2)                  |

| $fssv[b_{1111}] @750mV/850mV \{TT\} \\$             | MHz/V  | Equation (2)                  |

| FOM[b0000]@10kHz/100kHz/1MHz/10MHz{corner}          | dBc/Hz | Equation (1)                  |

| $FOM[b_{1111}]@10kHz/100kHz/1MHz/10MHz\{corner\}$   | dBc/Hz | Equation (1)                  |

## C. Optimization Objectives and Constraints

According to Table III, three optimization objectives were set to improve the worst-case corner performance from the worst-case mode, and, therefore, obtain the global optimum solutions. This is, minimize the largest power measured, minimize the worst value of phase noise at 10 MHz measured, and, minimize the highest *fssv* value measured. With this configuration the FOM is inherently optimized. Moreover, the third column of Table IV details the optimization constraints, which are set on the *fosc* to meet the desired 200 MHz range, at phase noises, and, FOMs. These optimization constraints were set for all corners. Additionally, only solutions with *fssvs* below 100 MHz/V were accepted.

TABLE III. OPTIMIZATION OBJECTIVES

| Target | Metric                                                                                                                                                                                                                                                                                                             | Units  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Min    | $\begin{array}{l} Max(power[b_{0000}]\{TT\}, power[b_{1111}]\{TT\},\\ power[b_{0000}]\{SS\}, power[b_{1111}]\{SS\},\\ power[b_{0000}]\{SF\}, power[b_{1111}]\{SF\},\\ power[b_{0000}]\{FS\}, power[b_{1111}]\{FS\},\\ power[b_{0000}]\{FF\}, power[b_{1111}]\{FF\}) \end{array}$                                   | mW     |

| Min    | $\begin{array}{l} Max(PN[b_{0000}]@10MHz\{TT\}, PN[b_{1111}]@10MHz\{TT\}, \\ PN[b_{0000}]@10MHz\{SS\}, PN[b_{1111}]@10MHz\{SS\}, \\ PN[b_{0000}]@10MHz\{SF\}, PN[b_{1111}]@10MHz\{SF\}, \\ PN[b_{0000}]@10MHz\{FS\}, PN[b_{1111}]@10MHz\{FS\}, \\ PN[b_{0000}]@10MHz\{FF\}, PN[b_{1111}]@10MHz\{FF\}) \end{array}$ | dBc/Hz |

| Min    | Max(fssv[b0000]@750mV, fssv[b0000]@850mV,<br>fssv[b1111]@750mV, fssv[b1111]@850mV)                                                                                                                                                                                                                                 | MHz/V  |

## D. Sizing Optimization: Results and Analysis

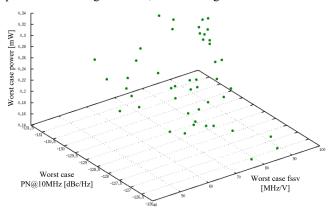

The circuit simulator adopted was the Mentor Graphics' Eldo RF. The optimization was carried with a population of 256 elements through 100 generations using the sizing optimization framework from [4]. Due to the time required to completely evaluate a candidate solution by 14 expensive SST analysis, even in a modern Intel-Xeon-CPU E5-2630-v3@2.40GHz workstation with 64GB of RAM, using 8 cores for parallel simulation, the optimization took approximately 367 hours. The maximum time allowed for each SST execution was 10 minutes. The worst-case corner of worst-case mode optimization provided 48 sizing solutions, drawn in Fig. 2.

Fig. 2. Pareto front with the tradeoff of Table III with 48 sizing solutions. The solutions spread from 0.145 mW to 0.329 mW power, -126.31 dBc/Hz to -131.11 dBc/Hz PN@10MHz, and, 40 MHz/V to 100 MHz/V *fssv*. The performances shown are the worst possible for each corner/mode of the design.

#### **III. AUTOMATIC LAYOUT GENERATION & RESULTS**

This section details the automatic layout generation.

## A. Hierarchichal Template-based Placer

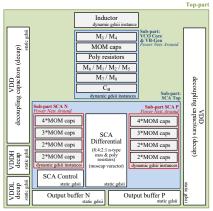

In this PDK, compact models used for simulation of RF devices contain complete layout parasitic information. Thus, the extraction of RF devices must be performed at gate-level, and, the layout instances used within automatic procedures should be identical to the ones provided by the foundry. In this revised version of the template-based approach for analog and RF IC blocks proposed in [8], to bypass the expensive development of custom generators for RF cells, the layout of all devices is imported as GDSII files. The designer is responsible for providing the high-level floorplan guidelines such as the ones presented in Fig. 3, capitalizing his expertise and layout preferences, e.g., aligned signal-flows, minimal wiring topology, guard-rings, dummies, etc. The hierarchical floorplan is built automatically, as the sub-partitions are generated first and combined at top partitions, given any set of device sizes.

## B. Group-based Routing

While the placement is controlled by the circuit designer using the specification-independent template, all routing tasks are performed automatically. Preliminarily, each terminal of each GSDII cell instantiated is parsed by the tool and made available for the routing procedure. Afterwards, three steps are performed sequentially: (1) the terminal-to-terminal connections are determined from the circuit netlist; (2) a global routing solution that incorporates symmetry information is devised; (3) and finally, a detailed optimization process is used to solve all design-rule and LVS errors [8]. Due to the high number of shapes laid out in the previous placement step and nets requiring to be routed, the detailed routing is particularly time-consuming, as built-in algorithms check the design-rules and short-circuits in every shape of the layout every time the optimization kernel performs a layer or structural change. To speed up this process, the 3-step routing procedure was separated into five independent processes exploiting the hierarchy of the placement template. This is, firstly, the sub-partitions SCA N and SCA P are internally routed, after, the SCA Top and VCO Core & VB-Gen, and finally, the routing of the top-partition, that interconnects the routed SCA Top, the routed VCO Core & VB-Gen, output buffers and decoupling capacitors.

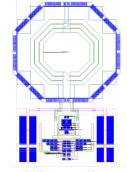

## C. Post-layout Performance

The automatic layout generation of each of the 48 solutions of Fig. 2 took over 2 hours. The layouts were saved as GDSII files, validated in Mentor Graphics' Calibre nmLVS®, extracted in Calibre xRC®, and, the post-layout performances simulated. The simulation times of the extracted netlists increase exponentially with respect to the pre-layout. In every design, at least one of the 14 testbenches failed convergence post-layout, making it impossible to evaluate its overall performance. In some cases, the extracted layout parasitics make the design stop oscillation as the simulator is unable to converge to the guessed oscillation frequency, whereas in others the simulation attempts to converge infinitely. The post-layout performances of one solution, corresponding to the pre-layout solution with worst case values of 0.267 mW power, -130.66 dBc/Hz PN@10MHz and 76 MHz/V *fssv*, are outlined in columns 4 to 8 of Table IV. The converging testbenches of this and each other 47 designs allowed to take valuable insights on the post-layout performance space, as the deviation from the desired oscillation frequency and drop on  $PNs[b_{1111}]$  are the most recurrent problems.

## D. Design Tuning

Since the computational times required by the automatic layout generation procedure and simulation of extracted netlist of 14 testbenches are still prohibitive for full layout-aware optimization, the highlighted solution was re-iterated by tuning the inductor and bias current. For that purpose, EDA tools were resorted again. The extracted netlist of the design was kept, and, an optimization that changes only the inductor dimensions (radius, turns, spacing and width) and IB current was carried with a population of 16 elements. The objectives and constraints of Section II. D were kept, and, the optimization was stopped when feasibility (i.e., all constraints satisfied) was achieved. In the last columns of Table IV, the post-layout performances of the reiterated design are outlined. The proposed solution achieved extremely low post-layout power consumption, 0.348 mW worst case, and, frequency pushing figures, 84 MHz/V worst case. The latest being extremely relevant as it is a critical issue in the design of VCOs for real-life product. The prototype was sent for fabrication as its post-layout performance compete in the forefront with most-recently published VCOs (Table I of [1]).

TABLE IV. MEASURES, OPTIMIZATION CONSTRAINTS AND POST-LAYOUT PERFORMANCES

|                                             | Units  | Torget                   | Post-layout                                                                         |                    |                    |                    | After Post-Layout Tuning                                                                     |                 |                    |        |        |                     |

|---------------------------------------------|--------|--------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------|-----------------|--------------------|--------|--------|---------------------|

| Measure                                     |        |                          | I <sub>B</sub> 10μA, <i>radius</i> 75μA, <i>turns</i> 3,<br>spacing 2μA, width 15μA |                    |                    |                    | I <sub>B</sub> <b>13μA</b> , radius <b>70μA</b> , turns 3,<br>spacing 2μA, width <b>14μA</b> |                 |                    |        |        |                     |

|                                             |        |                          | TT                                                                                  | SS                 | FS                 | SF                 | FF                                                                                           | TT              | SS                 | FS     | SF     | FF                  |

| f <sub>osc</sub> [b <sub>0000</sub> ]@800mV | GHz    | $\geq 5.3$<br>$\leq 5.5$ | 5.078 <sup>f</sup>                                                                  | 5.089 <sup>f</sup> | 5.089 <sup>f</sup> | 5.067 <sup>f</sup> | 5.067 <sup>f</sup>                                                                           | 5.316           | 5.305              | 5.327  | 5.305  | 5.328               |

| $f_{osc}[b_{1111}]@800mV$                   | GHz    | $\geq$ 4.4<br>$\leq$ 4.6 | <b>4.390</b> <sup>f</sup>                                                           | n/c                | 4.393 <sup>f</sup> | 4.387 <sup>f</sup> | <b>4.38</b> 7 <sup>f</sup>                                                                   | 4.588           | 4.578              | 4.592  | 4.584  | 4.598               |

| fssv[b0000]@750mV                           | MHz/V  | $\leq 100$               | 88                                                                                  | n/d                | n/d                | n/d                | n/d                                                                                          | 80              | n/d                | n/d    | n/d    | n/d                 |

| fssv[b0000]@850mV                           | MHz/V  | $\leq 100$               | 76                                                                                  | n/d                | n/d                | n/d                | n/d                                                                                          | 72              | n/d                | n/d    | n/d    | n/d                 |

| fssv[b1111]@750mV                           | MHz/V  | $\leq 100$               | 78                                                                                  | n/d                | n/d                | n/d                | n/d                                                                                          | 84 <sup>w</sup> | n/d                | n/d    | n/d    | n/d                 |

| fssv[b1111]@850mV                           | MHz/V  | $\leq 100$               | 62                                                                                  | n/d                | n/d                | n/d                | n/d                                                                                          | 72              | n/d                | n/d    | n/d    | n/d                 |

| PN[b0000]@10kHz                             | dBc/Hz | ≤-55                     | -62.8                                                                               | -63.6              | -62.7              | -63.2              | -61.8                                                                                        | -66.1           | -66.5              | -64.7  | -65.4  | -63.7               |

| PN[b0000]@100kHz                            | dBc/Hz | $\leq$ -80               | -88.0                                                                               | -88.2              | -88.0              | -88.1              | -87.6                                                                                        | -89.7           | -90.0              | -89.2  | -89.4  | -88.6               |

| PN[b0000]@1MHz                              | dBc/Hz | $\leq$ -100              | -109.3                                                                              | -109.2             | -109.4             | -109.3             | -109.4                                                                                       | -110.3          | -110.6             | -110.1 | -110.2 | -109.7              |

| PN[b0000]@10MHz                             | dBc/Hz | $\leq$ -120              | -129.5                                                                              | -129.3             | -129.5             | -129.5             | -129.7                                                                                       | -130.4          | -130.6             | -130.2 | -130.3 | -129.8              |

| PN[b1111]@10kHz                             | dBc/Hz | $\leq$ -60               | -60.4                                                                               | n/c                | -59.2 <sup>f</sup> | -61.9              | -62.2                                                                                        | -61.4           | -61.7              | -60.9  | -62.1  | -61.2               |

| PN[b1111]@100kHz                            | dBc/Hz | $\leq$ -80               | -85.5                                                                               | n/c                | -84.8              | -86.3              | -86.9                                                                                        | -86.8           | -87.3              | -86.5  | -87.2  | -86.3               |

| PN[b1111]@1MHz                              | dBc/Hz | $\leq$ -100              | -106.9                                                                              | n/c                | -106.4             | -107.3             | -108.1                                                                                       | -108.3          | -109.0             | -108.1 | -108.5 | -107.6              |

| PN[b1111]@10MHz                             | dBc/Hz | ≤ -120                   | -127.0                                                                              | n/c                | -126.6             | -127.4             | -128.3                                                                                       | -128.5          | -129.2             | -128.2 | -128.6 | -127.6 <sup>w</sup> |

| power[b <sub>0000</sub> ]                   | mW     | n/d                      | 0.246                                                                               | 0.291              | 2.415              | 0.250              | 0.267                                                                                        | 0.302           | 0.325              | 0.295  | 0.309  | 0.286               |

| power[b1111]                                | mW     | n/d                      | 0.251                                                                               | n/c                | 2.451              | 0.257              | 0.274                                                                                        | 0.322           | 0.348 <sup>w</sup> | 0.314  | 0.329  | 0.305               |

| FOM[b0000]@10kHz                            | dBc/Hz | $\geq 170$               | 183.0                                                                               | 184.1              | 183.0              | 183.3              | 181.6                                                                                        | 185.8           | 185.9              | 184.6  | 185.0  | 183.7               |

| FOM[b0000]@100kHz                           | dBc/Hz | $\geq 180$               | 188.2                                                                               | 188.7              | 188.3              | 188.3              | 187.5                                                                                        | 189.4           | 189.4              | 189.0  | 189.0  | 188.5               |

| FOM[b0000]@1MHz                             | dBc/Hz | $\geq 180$               | 189.5                                                                               | 189.7              | 189.7              | 189.4              | 189.2                                                                                        | 190.0           | 190.0              | 189.9  | 189.8  | 189.6               |

| FOM[b0000]@10MHz                            | dBc/Hz | $\geq 180$               | 189.7                                                                               | 189.8              | 189.9              | 189.6              | 189.5                                                                                        | 190.1           | 190.0              | 190.0  | 189.9  | 189.7               |

| FOM[b1111]@10kHz                            | dBc/Hz | $\geq 170$               | 179.2                                                                               | n/c                | 178.2              | 180.7              | 180.6                                                                                        | 179.5           | 179.5              | 179.1  | 180.2  | 179.6               |

| FOM[b1111]@100kHz                           |        |                          | 184.3                                                                               | n/c                | 183.8              | 185.0              | 185.4                                                                                        | 184.9           | 185.1              | 184.7  | 185.2  | 184.7               |

| FOM[b1111]@1MHz                             | dBc/Hz | $\geq 180$               | 185.7                                                                               | n/c                | 185.4              | 186.0              | 186.6                                                                                        | 186.4           | 186.8              | 186.3  | 186.5  | 186.0               |

| FOM[b <sub>1111</sub> ]@10MHz               | dBc/Hz | $\geq 180$               | 185.9                                                                               | n/c                | 185.6              | 186.1              | 186.7                                                                                        | 186.6           | 187.0              | 186.5  | 186.6  | 186.0               |

Fig. 3. Graphical representation of the template hierarchy used for the placement generation.

<sup>f</sup>Performances failing specification; <sup>w</sup>Worst-case performances; n/c the simulation did not converged;

# IV. CONCLUSION & FUTURE RESEARCH DIRECTIONS

EDA tools are long-known for dealing with problems beyond human capabilities, such as considering simultaneously a large amount of conflicting pre-/post-layout performance in the design of RF circuits. In this paper, the IoT-VCO proposed for a 65 nm PDK still hinders the straightforward application of layout-aware sizing tools, as it is pushing the computational capabilities of modern workstations to its limits. Nonetheless, the extensive use of automatic sizing and layout methodologies allowed to take a realistic insight of the post-layout potential of a several candidate sizing solutions, and, eased the process of obtaining a competitive design, that fulfills all specification, for further fabrication. As future research directions, it is desired to accurate electromagnetic-simulated [12] use inductor performances in-the-loop, as well as performing full layoutaware optimization. However, before committing to the latter, it is important to understand several aspects: (1) deciding when to stop simulator convergence attempts is a delicate decision. If stopped earlier, a promising solution may be lost. If a lot of CPU time is allowed without success, it may represent days/months of computational time lost; (2) the guessed oscillation frequencies in the SSTs have a direct effect in their output, as the same solution may converge or not by similar guessed frequencies. A possible work around is to optimize the guess frequency too or simulate multiple guesses; and (3), similarly, the layout generation may attain a solution with short-circuits, not necessarily meaning that the sizing solution was bad, but that the layout generation need to be re-optimized.

Fig. 4. Automatically generated layout.

## REFERENCES

- M. Shahmohammadi, et. al., "A 1/f Noise Upconversion Reduction Technique for Voltage- Biased RF CMOS Oscillators," in IEEE Journal of Solid-State Circuits, vol. 51, no. 11, pp. 2610–2624, Nov. 2016.

- [2] C.-C. Lim, et. al., "An inverse-class-F CMOS VCO with intrinsic-high-Q 1st- and 2nd-harmonic resonances for 1/f2-to-1/f3 phase noise suppression achieving 196.2dBc/Hz FoM," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 374-375, Feb. 2018.

- [3] R. Póvoa, et al., "LC-VCO automatic synthesis using multi-objective evolutionary techniques," in *IEEE ISCAS*, pp. 293-296, Jun. 2014.

- [4] R. Martins, et. al., "Many-Objective Sizing Optimization of a Class-C/D VCO for Ultralow-Power IoT and UltralowPhase-Noise Cellular Applications" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 1, pp. 69-82, Jan. 2019.

- [5] F. Passos, et. al., "Enhanced Systematic Design of a Voltage Controlled Oscillator using a Two-Step Optimization Methodology," Integration, the VLSI, vol. 63, pp. 351-361, Sept. 2018.

- [6] C. Ranter, et. al., "CYCLONE: automated design and layout of RF LCoscillators," *IEEE TCAD*, vol. 21, no. 10, pp. 1161-1170, Oct. 2002.

- [7] F. Passos, et. al., "Handling the Effects of Variability and Layout Parasitics in the Automatic Synthesis of LNAs," 15<sup>th</sup> Int. Conf. on SMACD, pp. 1-4, July 2018.

- [8] R. Martins, et. al., "Two-Step RF IC Block Synthesis with Pre-Optimized Inductors and Full Layout Generation In-the-loop" IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), May 2018 (Early Access). DOI: 10.1109/TCAD.2018.2834394

- [9] M. Tohidian et. al., "High-Swing Class-C VCO," in Proceedings of the ESSCIRC, pp. 495-498, Sept. 2011.

- [10] L. Fanori and P. Andreani, "A High-Swing Complementary Class-C VCO," 2013 Proc Esscirc, pp. 407–410, 2013.

- [11] M. Tohidian, A. Fotowat-Ahmadi, M. Kamarei, and F. Ndagijimana, "High-Swing Class-C VCO," 2011 Proc Esscirc, pp. 495–498, 2011.

- [12] Sonnet Suite 16, Sonnet Software, Inc., http://www.sonnetsoftware.com.