# Split-SAR ADCs: Improved Linearity With Power and Speed Optimization

Yan Zhu, Chi-Hang Chan, U-Fat Chio, Sai-Weng Sin, Seng-Pan U, Rui Paulo Martins, and Franco Maloberti

Abstract—This paper presents the linearity analysis of a successive approximation registers (SAR) analog-to-digital converters (ADC) with split DAC structure based on two switching methods: conventional charge-redistribution and  $V_{\rm cm}$ -based switching. The static linearity performance, namely the integral nonlinearity and differential nonlinearity, as well as the parasitic effects of the split DAC, are analyzed hereunder. In addition, a code-randomized calibration technique is proposed to correct the conversion nonlinearity in the conventional SAR ADC, which is verified by behavioral simulations, as well as measured results. Performances of both switching methods are demonstrated in 90 nm CMOS. Measurement results of power, speed, and linearity clearly show the benefits of using  $V_{\rm cm}$ -based switching.

*Index Terms*—Linearity analysis, linearity calibration, SAR ADCs, split DAC, V<sub>cm</sub>-based switching.

#### I. Introduction

UCCESSIVE approximation registers (SAR) analog-to-digital converters (ADCs) [1]–[4], as an alternative to the pipelined ADCs [5]-[9] has become popular for battery-powered mobile applications, such as DVB-T, DVB-H and TDMB [10], [11] which require medium speed (10 MS/s-100 MS/s) and medium-resolution (8-10 b). SAR ADCs [2]–[4] achieve very low power consumption due to their simple architecture and operation. However, the SAR conversion relies basically on the performance of a capacitive DAC that subtracts the reference voltage from the input signal. The kT/C noise, capacitor mismatches, and parasitic of the split DAC [12] affect the conversion accuracy. As for medium resolution, the kT/C noise requirement is fulfilled with small capacitance, while other nonidealities like parasitic and nonlinearity, whose effect depends on the structure and the switching approach of the DAC, becomes significant.

Manuscript received May 29, 2012; revised December 13, 2012; accepted January 8, 2013. Date of publication February 14, 2013; date of current version January 17, 2014. This work was supported in part by the Research Committee of the University of Macau and the Macao Science and Technology Development Fund.

Y. Zhu, C.-H. Chan, U. F. Chio, S. W. Sin, and S. P. U are with the State-Key-Laboratory Analog and Mixed-Signal VLSI, Faculty of Science and Technology, University of Macau, Macao 853, China (e-mail: yanjulia@ieee.org).

R. P. Martins is with the State-Key-Laboratory Analog and Mixed-Signal VLSI, Faculty of Science and Technology, University of Macau, Macao 853, China, and also with the Instituto Superior Técnico/TU, Lisbon 1049-001, Portugal (e-mail: rmartins@umac.mo).

F. Maloberti is with the Department of Electronics, University of Pavia, Pavia 27100, Italy (e-mail: franco.maloberti@unipv.it).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2013.2242501

The binary-weighted capacitive DAC is widely used in SAR ADCs. However, the capacitance of the DAC array increases exponentially with the resolution, which imposes larger consumption of switching energy, area, and settling time. A valuable substitute is the split capacitive DAC, which has been recently reconsidered for medium resolution [13]–[18]. Its key limitation lies in the parasitic capacitors that destroy the desired binary ratio of the capacitive DAC array, thus degrading the conversion linearity. However, by using the metal-insulator-metal (MIM) capacitor or/and DAC mismatch calibrations [19]–[22], the split structure can become suitable for a medium-resolution target. On the other hand, the conversion linearity is also directly correlated with the switching sequences of the DAC array [12], [23], where the conventional charge-redistribution switching results in worse conversion linearity and more energy losses. A V<sub>cm</sub>-based switching technique has been recently proposed [24], which achieves a significant switching energy saving when compared with set-and-down [3] and charge-recycling [25] switching approaches.

This paper analyzes the conversion nonlinearities, induced by supply noise, switching methods, and parasitic effects in SAR ADCs. The static nonlinearities based on the conventional and  $V_{\rm cm}$ -based [24] switching methods are theoretically analyzed, and the mathematical models are developed to verify the effectiveness of the  $V_{\rm cm}$ -based approach. Experimental results on a 90 nm CMOS 10 b 65 MS/s SAR ADC with conventional switching and a 10 b 100 MS/s SAR ADC with  $V_{\rm cm}$ -based switching demonstrate the performance benefits in terms of speed, power, and linearity by using  $V_{\rm cm}$ -based switching.

In addition, the internal node parasitic in the split DAC is also analyzed, as it degrades the conversion linearity. The above limitation can be fixed by a code-randomized digital calibration technique proposed here to improve the differential nonlinearity (DNL) and integral nonlinearity (INL).

Section II presents the overall SAR ADC architecture; Section III introduces the conventional and  $V_{\rm cm}$ -based switching approaches. Section IV provides an analytical analysis of the static nonlinearity due to the capacitor mismatch and the parasitic effects in the two methods, and it also includes the behavioral simulations for confirmation of results. Finally, a DNL and INL calibration technique for parasitic nonlinearity in split DAC is proposed in section V. The measurement results of two integrated SAR ADCs and the conclusions are presented in Sections VI and VII, respectively.

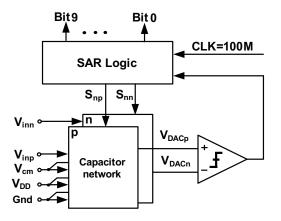

Fig. 1. Block diagram of the ADC architecture.

#### II. OVERALL ADC ARCHITECTURE

Fig. 1 shows the architecture of the 10 b ADC. It is a conventional SAR ADC [24] consisting of a differential capacitive network a comparator and SA control logic. The SAR logic includes shift registers [26] and switch drivers which control the DAC operation by performing a binary-search algorithm during the conversion cycle. The capacitive DAC array is the basic structure of the SA ADC, which serves both to sample the input signal and subtract the reference. A reference-buffer-free technique [24] is used to improve the power dissipation and DAC settling. As the supplies  $V_{\rm DD}$  and Gnd are used directly as reference voltages, the conversion sensitivity to supply variation is quantitatively analyzed in the Appendix.

## III. SWITCHING METHODS

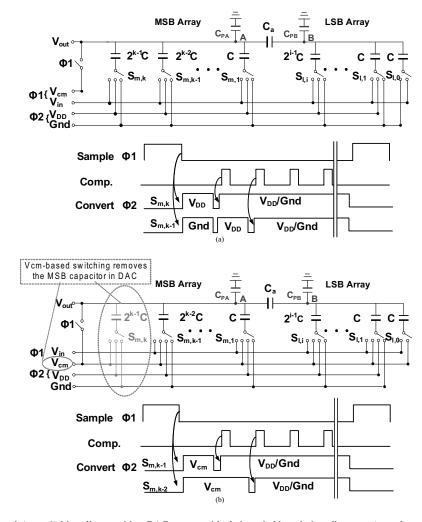

When using the supplies as reference, the switching power is dynamic, which is correlated with the switching sequence Fig. 2(a) shows a conventional single-ended n-bit split [k-bit most significant bit (MSB) and i-bit LSB sub-array] DAC structure and its switching timing diagram. During the global sampling phase, the input signal  $V_{\rm in}$  is stored in the entire capacitor array. The algorithmic conversion then begins by switching only the MSB capacitor to  $V_{\rm DD}$  and the others to Gnd. Accordingly,  $V_{\rm out}$  settles to  $-V_{\rm in}$  and the comparator output Out\_{comp} in the first MSB decision will be

$$\mbox{Out-\{comp\}} = \left\{ \begin{array}{cc} 0 & V_{in} > 0 \\ 1 & V_{in} < 0. \end{array} \right. \eqno(1)$$

The comparator output decides the switching logic of the MSB capacitor. If  $Out_{comp}$  is low  $S_{m,k}$  is switched back to Gnd If  $Out_{comp}$  is high, then  $S_{m,k}$  is kept to  $V_{DD}$ . For either decision, simultaneously, the  $S_{m,k-1}$  (the MSB/2) switches to  $V_{DD}$  for the next bit comparison. The above process will be repeated for n-1 cycles.

The conventional charge-redistribution method is not very power effective [25], especially when discharging the MSB and charging the MSB/2 capacitor is required (bit decision back from "1" to "0") This is unnecessary in general, but it is required for that specific technique to operate properly.

However, it would be beneficial if it can be avoided to save switching energy.

The  $V_{\rm cm}$ -based switching method proposed in [24] halves the array capacitance leading to around 90% energy saving when compared with the conventional one. Fig. 2(b) details the  $V_{\rm cm}$ -based switching algorithm. In the global sampling phase  $\Phi_1$ ,  $V_{\rm in}$  is stored in the capacitor array. During the conversion phase  $\Phi_2$ , all the capacitors' bottom-plates are switched to the  $V_{\rm cm}$  first, to give rise to the voltage  $-V_{\rm in}$  at the output. The sign of  $V_{\rm out}$  determines the MSB as the logic properly controls  $S_{\rm m,k-1}$ . If  $-V_{\rm in} < 0$ ,  $S_{\rm m,k-1}$  goes to Gnd while the other switches  $S_{\rm m,k-2}$ , ...,  $S_{\rm l,0}$  remain connected to  $V_{\rm cm}$ . If  $-V_{\rm in} > 0$ ,  $S_{\rm m,k-1}$  is switched to  $V_{\rm DD}$ . The cycle will be repeated for n-2 times.

The  $V_{\rm cm}$ -based approach performs the MSB transition by connecting the differential arrays to  $V_{\rm cm}$ . The power dissipation is just derived from what is needed to drive the bottom-plate parasitic of the capacitive arrays, while in the conventional charge-redistribution where the necessary MSB "up" transition costs significant switching energy and settling time. Moreover, as the MSB capacitor is not required anymore, it can be removed from the n-bit DAC array. Therefore, the next n-1 b estimation is done with an (n-1) bit array instead of its n-bit counterpart, leading to half capacitance reduction with respect to the conventional method.

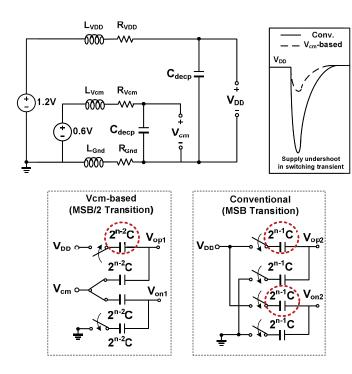

Using supplies as reference voltages prevents static power dissipation from reference buffers [3], [17], [24], although the conversion becomes very sensitive to the supply ripple due to the switching effect. For 10-b accuracy the supply variation needs to be suppressed within  $\pm 0.049\%$  of the full supply rail, or the supply ripple  $\pm 588 \mu V$  for a 1.2 V supply. The detailed analysis of conversion sensitivity to supply noise is presented in the Appendix. As the  $V_{\rm cm}$ -based switching charges 75% less capacitance, simultaneously, when compared with the conventional switching, it can effectively reduce the under-shoot of the supply or reference buffer (when used). The inductive ringing effect can be well suppressed by minimizing the bonding inductance, e.g., multiple bonding, through the addition of a damping resistor and an on-chip decoupling capacitor  $C_{\text{decp}}$ . On the other hand, to overcome this problem an effective approach might be the use of a SA searching algorithm like nonbinary conversion [27] that relaxes the settling accuracy requirement during large switch transients.

## IV. LINEARITY ANALYSIS

## A. Effect of Switching Schemes on the Linearity

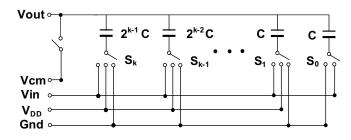

To analyze the conversion linearity of the conventional and the  $V_{\rm cm}$ -based switching methods in a binary-weighted DAC (shown in Fig. 3) each of the capacitors is modeled as the sum of the nominal capacitance value and the error term

$$C_n = 2^{n-1}C + \delta_n \tag{2}$$

considering that all the errors are in the unit capacitors, whose values are independent-identically distributed Gaussian random variables, and have a variance of

$$E[\delta_n^2] = 2^{n-1}\sigma^2 \tag{3}$$

Fig. 2. Single-ended n-bit and (n-1)-bit split capacitive DAC arrays with their switching timing diagrams (n=k+i). (a) Conventional switching. (b) V<sub>cm</sub>-based switching.

Fig. 3. k-bit binary-weighted DAC.

and where  $\sigma$  is the standard deviation of the unit capacitor. The  $V_{\rm cm}$ -based method achieves half capacitance reduction when compared with the conventional one, while the switching linearity comparison between the two switching methods should be addressed in the same capacitive DAC, with the same value of capacitor mismatch as well as predictable gain errors caused by unbalanced array capacitance. Accordingly, to perform the  $V_{\rm cm}$ -based switching method in the k-bit DAC array of Fig. 3, both  $S_0$  and  $S_1$  are kept connected to  $V_{\rm cm}$ during bits cycling.

To calculate a given digital input X with its corresponding DAC output  $V_{\text{out}}$  (X), the array is considered initially discharged ( $V_{in} = 0$ ). The analog output of the k-bit capacitive DAC with conventional switching can be calculated as

$$V_{\text{out}}(X) = \frac{\sum_{n=1}^{k} (2^{n-1}C + \delta_n)S_n + (C + \delta_0)S_0}{2^kC + \sum_{n=0}^{k} \delta_n} \cdot V_{\text{DD}}$$

(4)

where the DAC digital input  $X = [S_n...S_0]$ , with  $S_n$  equal to 1, 1/2 or 0 represents the DAC connecting  $V_{\rm DD}$ , 1/2  $V_{\rm DD}$ (i.e.,  $V_{cm}$ ) or Gnd for bit n. For a single channel SAR ADC, the comparator offset and linear gain error in the DAC are acceptable, thus closed form calculations of INL and DNL are specified with respect to a bestfit line. In the SAR conversion, the comparator offset appears as an offset error and does not cause nonlinearity, therefore, excluding the offset term, the INL and DNL are [28]

$$INL = \frac{V_{\text{out}}(X)/A - V_{\text{idl}}(X)}{I.SB}$$

(5)

$$DNL = \frac{[V_{out}(X) - V_{out}(X-1)]/A - LSB}{LSB}$$

(6)

INL =

$$\frac{V_{\text{out}}(X)/A - V_{\text{idl}}(X)}{\text{LSB}}$$

(5)

DNL =  $\frac{[V_{\text{out}}(X) - V_{\text{out}}(X - 1)]/A - \text{LSB}}{\text{LSB}}$  (6)

$$A = \frac{\sum_{X=0}^{2^{n-1}} V_{\text{out}}(X) \cdot V_{\text{idl}}(X)}{\sum_{X=0}^{2^{n-1}} V_{\text{idl}}^2(X)}$$

(7)

where A indicates the linear gain error of the DAC,  $V_{\text{idl}}(X)$  is the nominal value for the digital input X and LSB =  $1/2^k V_{DD}$ .

From (7), it can be deduced that the linear gain error A is input X dependent, which implies that the gain error  $A_{\rm con}$  for conventional switching and  $A_{\rm CM}$  for  $V_{\rm cm}$ -based one are not equivalent. However,  $A_{\rm con}$  and  $A_{\rm CM}$  values are quite close as 1000-time Monte Carlo simulations running in a 10-b DAC, where unit capacitors are Gaussian random variables with standard deviation of  $\sigma(\Delta C/C=1\%)$ , lead to variances of gain  $\delta_{\rm Acon}=\pm$  41e-5 and  $\delta_{\rm ACM}=\pm$  4.2e-5. Hence, to simplify the analysis, it will be assumed that the prospective linear gain A and the  $\delta$  terms in the denominator of (4) will be neglected.

The INLs of the two switching methods represent the conversion error that combines together all the errors in each bit. Considering that in  $V_{\rm cm}$ -based switching, the transitions are  $V_{\rm cm}$  related (with capacitors connected to  $V_{\rm cm}$ ), it follows that the INLs of the two switching methods must be different. First, the worst INL in conventional switching happens at the MSB transition [23], where only the MSB is pre-charged to  $V_{\rm DD}$ , leaving other capacitors to Gnd. For the  $V_{\rm cm}$ -based switching MSB transition is performed by level shifting all capacitors to  $V_{\rm cm}$ , which is input independent and ideally always achieves an INL of 0 LSB in the middle. The worst INL of  $V_{\rm cm}$ -based switching happens at the step below the MSB transition, where the input digital code is X = [10...0]. The corresponding input digital code of conventional switching is X = [10...1] The DAC output  $V_{out}(X)$  and INL of the conventional method INLcon are calculated as

$$V_{\text{out}}(X) = \frac{2^{k-1}C + \delta_k + C + \delta_1}{2^k C} \cdot V_{\text{DD}}$$

(8)

$$INL_{con} = \frac{\delta_k + \delta_1}{2^k C} \cdot \frac{V_{DD}}{LSB} = \frac{\delta_k + \delta_1}{C}$$

(9)

with variance

$$E[\delta_{\text{INLcon}}^2] = \frac{(2^{k-1} + 1)\sigma^2}{C^2}.$$

(10)

The INL of the  $V_{\rm cm}$ -based method INL<sub>CM</sub> and its variance  $E[\delta_{\rm INLCM}^2]$  can be similarly derived as follows:

$$INL_{CM} = \frac{\delta_k}{2^k C} \cdot \frac{V_{DD}}{LSB} = \frac{\delta_k}{C}$$

(11)

$$E[\delta_{\text{INL}_{\text{CM}}}^2] = \frac{2^{k-1}\sigma^2}{C^2}.$$

(12)

Comparing the results of (10) and (12) it proves that the conventional and  $V_{\rm cm}$ -based switching have similar INLs at the step below MSB transition. In reality,  $V_{\rm cm}$ -based switching is insensitive to the input common mode noise.

The maximum DNL for the conventional method is expected to occur at the step below the MSB transition. With X = [10...0] and (X - 1) = [01...1], the difference between the voltage errors can be calculated

as

$$V(X) - V(X - 1) = \frac{C + \delta_k - \sum_{n=1}^{k-1} \delta_k}{2^k C}$$

$$V_{DD} = LSB + \frac{\delta_k - \sum_{n=1}^{k-1} \delta_k}{C} \cdot LSB \quad (13)$$

thus, its DNL yields

$$DNL_{con} = \frac{\delta_k - \sum_{n=1}^{k-1} \delta_n}{C}$$

(14)

and with its variance

$$E[\delta_{\text{DNLcon}}^2] = \frac{(2^k - 1)\sigma^2}{C^2}.$$

(15)

In the  $V_{\rm cm}$ -based switching the MSB "up" transition is replaced by an initial reset of all the capacitors to  $V_{\rm cm}$  (with the middle digital input X equal to [1/2...1/2]). There exist two consecutive worst DNLs occurring at the steps above (X+1)=[0,1...1] and below (X-1)=[1,0...0] the MSB transition. One of the worst DNL<sub>CM</sub> with two digital inputs X=[1/2...1/2] and (X-1)=[0,1...1] is obtained similarly as

$$V(X) - V(X - 1) = LSB + \frac{1/2 \sum_{n=0}^{k} \delta_n - \sum_{n=0}^{k-1} \delta_n}{C} \cdot LSB$$

(16)

$$DNL_{CM} = \frac{1/2\delta_k - 1/2\sum_{n=0}^{k-1}\delta_n}{C}$$

(17)

with variance

$$E[\delta_{\text{DNL}_{\text{CM}}}^2] = \frac{2^k \sigma^2}{4C^2}.$$

(18)

Equations (15) and (18) show that the proposed method can achieve a DNL that is two times better in comparison to conventional switching. It can also be found that the error terms are decreased by half, which can be attributed to the cancellation of the terms  $\sum_{n=0}^{k-1} \delta_n$  in (16). In fact, this happens because the capacitors contributing to two-bit transitions are correlated, which are switched from  $V_{\rm cm}$  to  $V_{\rm DD}$ . In contrast, in the conventional method the capacitors connected to  $V_{\rm DD}$  in two-bit transitions are completely different, and the error terms in (13) are summed together instead of being cancelled.

# B. Effect of Parasitic Capacitors on Linearity of a Split DAC

The inherent linearity errors become worse when the split DAC array is used [12], [29]. The parasitic capacitance  $C_{\rm PA}$  and  $C_{\rm PB}$  in nodes A and B [shown in Fig. 2(a)] will deteriorate the desired voltage division ratio and degrade the conversion accuracy. The analog output  $V_{\rm out}$  (X) of a split DAC with  $C_{\rm PA}$  and  $C_{\rm PB}$  taken into account can be calculated as shown in (19) at the bottom of the page, where  $C_{\rm SL}$  and  $C_{\rm SM}$  is the sum of the capacitance in LSB and MSB arrays,

(19)

$$V_{\text{out}}(X) = \frac{C_{\text{a}}\left(\sum_{n=1}^{i} 2^{n-1}CS_{l,n} + CS_{l,0} + \sum_{n=1}^{k} 2^{n-1}CS_{m,n}\right) + (C_{\text{SL}} + C_{\text{PB}})\sum_{n=1}^{k} 2^{n-1}CS_{m,n}}{C_{\text{a}}(C_{\text{SL}} + C_{\text{PM}} + C_{\text{PA}} + C_{\text{PB}}) + (C_{\text{SL}} + C_{\text{PB}})(C_{\text{SM}} + C_{\text{PA}})} \cdot V_{\text{DD}}$$

respectively. The parasitic capacitor  $C_{PB}$  in the numerator changes the value of second term. The  $C_{PA}$  and  $C_{PB}$  in the denominator cause a gain error which is irrelevant in the analysis. Subtracting the nominal value, the error term of the MSB/2 transition (X = [010...0]) in the conventional method is given by

$$V_{\rm err}(X)_{\rm con} = \frac{C_{\rm PB} 2^{k-2} C}{C_{\rm a}(C_{\rm SL} + C_{\rm SM}) + C_{\rm SL} C_{\rm SM}} \cdot V_{\rm DD}.$$

(20)

Correspondingly, for the  $V_{\rm cm}$ -based method, the error term at the MSB/2 transition (X = [0, 1/2...1/2]) is obtained as

$$V_{\text{err}}(X)_{\text{CM}} = \frac{C_{\text{PB}}(2^{k-1}-1)C}{C_{\text{a}}(C_{\text{SL}}+C_{\text{SM}})+C_{\text{SL}}C_{\text{SM}}} \cdot \frac{V_{\text{DD}}}{2}$$

$$= \frac{C_{\text{PB}}(2^{k-2}-1/2)C}{C_{\text{a}}(C_{\text{SL}}+C_{\text{SM}})+C_{\text{SL}}C_{\text{SM}}} \cdot V_{\text{DD}}. \tag{21}$$

From (20) and (21), it can be concluded that the  $V_{\rm cm}$ -based and the conventional switching have a similar INL.

The increased DNL due to the  $C_{PB}$  is expected to happen at the step below the last bit transition of the MSB array. Considering the 10-b split DAC of Fig. 2(a) with 5 b of MSB array and 5 b of LSB array, two consecutive digital inputs for the conventional method are:  $X = [0000100000] \rightarrow (X - 1) = [0000011111],$  and 1/2]  $\rightarrow (X - 1) = [0000011111]$ . On the other hand, the error term  $C_{PB}$  in (19) is only correlated with the bits in the MBS array. Accordingly, the difference between the two voltage errors is only caused by the bit  $S_{m,1}$  in X. In conclusion, the voltage errors for conventional and  $V_{\rm cm}$ -based switching can be simply derived as

$$V_{\text{err,con}} = \frac{C_{\text{PB}}C}{C_{\text{e}}(C_{\text{SL}} + C_{\text{SM}}) + C_{\text{SL}}C_{\text{SM}}} \cdot V_{\text{DD}}$$

(22)

$$V_{\rm err,con} = \frac{C_{\rm PB}C}{C_{\rm a}(C_{\rm SL} + C_{\rm SM}) + C_{\rm SL}C_{\rm SM}} \cdot V_{\rm DD}$$

(22)

$$V_{\rm err,CM} = \frac{C_{\rm PB}C}{C_{\rm a}(C_{\rm SL} + C_{\rm SM}) + C_{\rm SL}C_{\rm SM}} \cdot \frac{V_{\rm DD}}{2}.$$

(23)

As a consequence of (22) and (23),  $V_{\rm cm}$ -based switching reduces the DNL by half when compared with the conventional switching. This benefit can be explained by the switching nature of the V<sub>cm</sub>-based method, which divides half of the voltage contribution from the last bit of the MSB array, which is C<sub>PB</sub> related, to all the capacitors in the LSB array that are irrelevant to  $C_{PB}$ . Table I summarizes the switching linearity of the two methods.

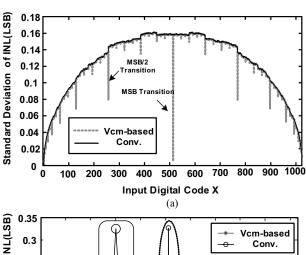

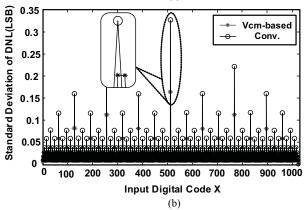

#### C. Behavioral Simulations

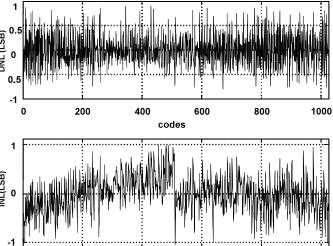

To verify the previous analysis, behavioral simulations were performed which modeled the conversion linearity of the conventional and  $V_{\rm cm}$ -based switching methods in a 10 b split DAC array with 5 b MSB and 5 b LSB arrays. The values of the unit capacitor are Gaussian random variables with a standard deviation of  $\sigma$  ( $\Delta C/C = 1\%$ ), and the parasitic capacitance is not considered. Fig. 4 illustrates the result of 1000-sample Monte Carlo runs, where the standard deviations of DNLs and INLs with respect to a best fit line are plotted versus the DAC input code at 10-b level. As expected, two methods have similarly large INLs, while  $V_{\rm cm}$ -based switching has lower INLs at the transitions where the input code is more relevant to  $V_{\rm cm}$ . This happens in the cases like the transitions

TABLE I SWITCHING LINEARITY COMPARISON BETWEEN CONVENTIONAL & VCM-BASED METHODS

| Switch Scheme                                                                                  | k-bit Binary DAC                  |                               | (k+i)-bit Split DAC |                   |

|------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------|---------------------|-------------------|

|                                                                                                | $E[\delta_{INL}^2]$               | $E[\delta_{	extit{DNL}}^2]$   | $V_{\it err,INL}$   | $V_{\it err,DNL}$ |

| Conventional                                                                                   | $\frac{(2^{k-1}+1)\sigma^2}{C^2}$ | $\frac{(2^k-1)\sigma^2}{C^2}$ | $2^{k-2}T$          | T                 |

| V <sub>cm</sub> -based                                                                         | $\frac{2^{k-1}\sigma^2}{C^2}$     | $\frac{2^k \sigma^2}{4C^2}$   | $(2^{k-2}-1/2)T$    | $\frac{T}{2}$     |

| $ \sqrt{\frac{E[\mathcal{S}_{con}^2]}{E[\mathcal{S}_{CM}^2]}} \frac{V_{err,con}}{V_{err,CM}} $ | ≈1                                | ≈2                            | ≈1                  | 2                 |

**Note:**

$$T = \frac{C_{PB}C}{C_a(C_{SL} + C_{SM}) + C_{SL}C_{SM}} \cdot V_{DD}$$

Fig. 4. Behavioral simulation comparing the DNL and INL of conventional and  $V_{\rm cm}$ -based 10-b SAR ADCs.

of MSB and MSB/2. The DNL plot shown in Fig. 4(b) confirms the presented analysis of  $V_{\rm cm}$ -based switching that denotes two consecutive high DNLs at the middle. Their value is two times lower than its conventional counterpart.

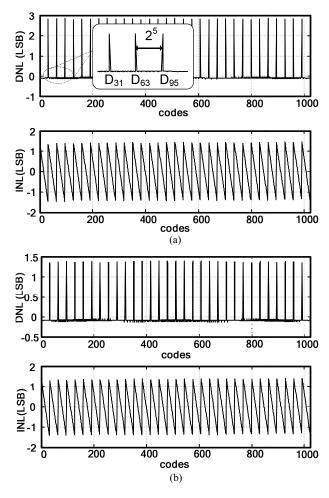

The simulation estimates the effect of the parasitic capacitor in the split structure supposing 10% top-plate parasitic with matched capacitor. The DNLs and INLs results of conventional and  $V_{\rm cm}$ -based switching methods obtained by 100 000 points with sine wave input are shown in Fig. 5. The maximum DNLs and INLs of conventional and  $V_{\rm cm}$ -based switching are 2.9

Fig. 5. Behavioral simulation results of DNLs and INLs for 10-b SAR ADCs with  $C_{\rm PB}$ . (a) Conventional switching. (b)  $V_{\rm cm}$ -based switching.

LSB/1.5 LSB and 1.4 LSB/1.4 LSB, respectively. In Fig. 5, it can be found that the ratio mismatch between the MSB and LSB arrays, caused by  $C_{PB}$ , results in the large quantization errors, which happen periodically at the carry from LSB array to the MSB array. Consequently, the interval between two large quantization steps is  $2^5$ .  $V_{cm}$ -based method has two times better DNL than conventional while the INLs of the two methods are quite similar.

### V. DNL AND INL CALIBRATION TECHNIQUE

In practice, the conversion nonlinearity gets worse when the conventional switching is used. Since there is a large switching transient in its "down" transition, caused by switching two capacitors simultaneously, the large switching transient causes the excessive supply voltage undershoot as well as potentially exacerbates an overdrive condition of the preamplifier, which will finally result in a wrong decision on the comparator's output. In contrast,  $V_{\rm cm}$ -based switching prevents occurrence of such large switching transient. In every bit cycle, only one capacitor is switched to obtain a voltage value by successive approximation of the input voltage without wasting energy and settling time. Moreover, the mismatches of the attenuation capacitor, as well as, the routing parasitic capacitance in the internal node of the DAC, cause conversion nonlinearity.

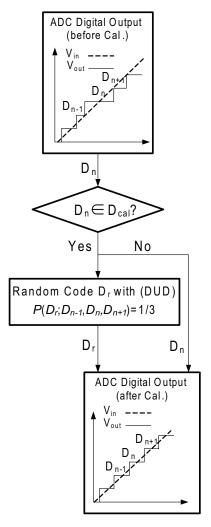

Fig. 6. Code-randomized calibration algorithm.  $D_{\rm r}$  has discrete uniform distribution (DUD), which implies the probability (P) of any outcome  $D_{\rm r}$  from three possible values  $D_{n-1}$ ,  $D_n$ ,  $D_{n+1}$  is 1/3.

From Fig. 5, it can be seen that the nonlinearity is a static conversion error, which happens periodically corresponding to the number of bits distributed in the LSB array. Therefore, the foreseeable static linearity errors can be potentially calibrated in the digital domain.

Ideally all the quantization levels of the *n*-bit ADC are uniformly spaced, but due to nonideal elements in the actual circuit implementation the code transition points in the transfer function will be moved shown in Fig. 6. To calibrate the linearity error, a code-randomized calibration is proposed, which provides a plausible digital post-processing to fix the large quantization errors. This is achieved by redistributing the steps with statistically equally over the step's  $\pm$  LSB range. The calibration algorithm is shown in Fig. 6. The digital outputs used to find the DNL and INL errors are compensated values, where the comparator offset and linear gain errors will not appear. First the calibration will determine whether the ADCs digital output needs to be corrected. For an n-bit ADC with the split DAC shown in Fig. 2(a) there are m $(m = 2^n/2^i - 1)$  digital codes  $(D_{cal} = [D_1, D_2, ..., D_m]),$ where large quantization steps happen and they are subject

Fig. 7. Calibrated DNL and INL of SAR ADC with conventional switching.

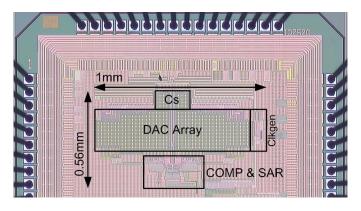

Fig. 8. Die microphotograph of the SAR ADC with conventional switching.

to be calibrated. When the ADCs digital output  $D_{\rm n}$  matches any of the digital code in  $D_{\rm cal}$ , the random number generator will outcome a new digital output  $D_{\rm r}$ . The randomized output  $D_{\rm r}$  has one of the three possible values  $D_{\rm n}$  and its two adjacent quantization levels  $D_{\rm n-1}$  and  $D_{\rm n+1}$ , which are equally spaced with an identical probability of 1/3. The randomized solution transfers the nonlinearity into increased average quantization noise power. Therefore, the large DNL and INL errors can be calibrated with signal-to-noise distortion ratio (SNDR) of the ADC dropping slightly. Verified by a behavior simulation of a 10 b level, the SNDR with and without code-randomized calibration is 56.2 and 55.6 dB, respectively (32768 samples are taken in a 10-b SAR ADC with 10% top-plate parasitic  $C_{\rm PB}$ , while ADC is otherwise ideal).

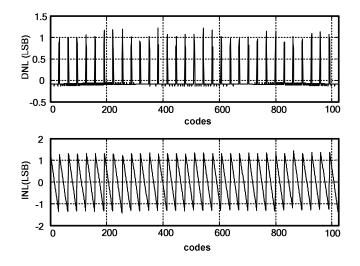

The code-randomization calibration is used to calibrate the DNL errors shown in Fig. 5(a). For example, when the output digital code  $D_{31}$  is detected, the system will auto-generate a new digital output selected from the codes  $D_{30}$ ,  $D_{31}$ , and  $D_{32}$ . Fig. 7 exhibits the calibrated DNL and INL results, where the maximum DNLs and INLs of the conventional method are both improved from 2.9 LSB to 1.3 LSB and 1.5 LSB to 1.4 LSB, respectively.

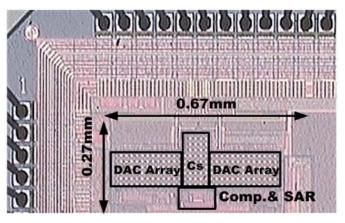

Fig. 9. Die microphotograph of the SAR ADC with  $V_{\rm cm}$ -based switching.

Fig. 10. FFTs of the digital outputs with input at 1.8 MHz. (a) Conventional SAR ADC sampled at 65 MS/s. (b)  $V_{\rm cm}$ -based SAR ADC sampled at 100 MS/s.

## VI. MEASUREMENT RESULTS

Two 1.2 V 10-b SAR ADCs were fabricated in 90 nm CMOS for conversion linearity comparison. The first chip is a 10-b 65 MS/s SAR ADC with conventional switching, while the second chip is a 10-b 100 MS/s SAR ADC with  $V_{\rm cm}$ -based switching. The die micrographs of the two ADCs are shown in Figs. 8 and 9. 10-b (conventional) and 9-b (the MSB capacitance is removed due to the advantages of  $V_{\rm cm}$ -based switching) split DAC arrays were implemented to verify switching efficiency. The unit capacitance of a MIM capacitor is 50 fF, and the value of the attenuation capacitor  $C_a$  is 53.3 fF that is 16/15 unit. The  $C_s$  capacitor shown in Figs. 8 and 9 is used to implement the reference-buffer-free technique [24] with a capacitance of 400 fF. On the other hand, MIM capacitors exhibit very low top-plate parasitic, estimated to be <5%. The active areas of the conventional and  $V_{\rm cm}$ -based ADC are 0.56 and 0.18 mm<sup>2</sup>, respectively.

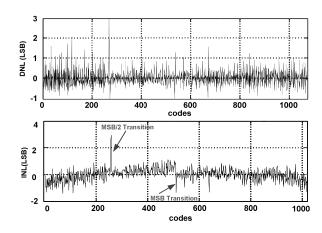

Fig. 11. Measured INL and DNL of 10-b SAR ADC with conventional switching.

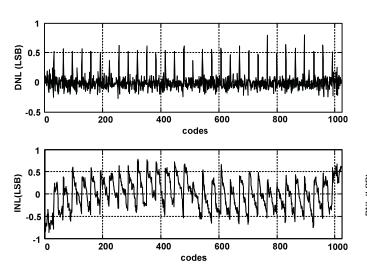

Fig. 12. Measured INL and DNL of 10-b SAR ADC with  $V_{\rm cm}$ -based switching.

Fig. 10 shows output spectrums of the two ADCs with the input frequency at 1.8 MHz. The conventional SAR ADC can achieve 8.6 b ENOB at a sampling rate of 65 MS/s. When the  $V_{\rm cm}$ -based approach is utilized, the ADC can achieve 100 MS/s sampling rate and the ENOB is improved to 9.1 b.

The measured DNL and INL of the ADC with conventional and  $V_{\rm cm}$ -based switching are illustrated in Figs. 11 and 12, respectively. The experimental measurements verify the benefits of  $V_{\rm cm}$ -based switching approach that exhibits a lower DNL and INL when compared with the conventional one. By utilizing  $V_{\rm cm}$ -based switching, the maximum DNL and INL are improved from 3 to 0.79 LSB and from 2.8 to 0.86 LSB, respectively. The INL from Fig. 12 is s-like and is minimized in the middle, while in Fig. 11, it is quite large in both MSB and MSB/2 transitions. The advantage of  $V_{\rm cm}$ -based switching stems from the MSB decision's independence of the capacitor mismatch. This was discussed in Section IV-A.

Fig. 11 shows that the high spikes are not symmetrically distributed. This is mainly caused by the large switching transients leading to insufficient DAC settling and supply ripples. The effect of parasitic capacitors of a split DAC

TABLE II

SUMMARY OF PERFORMANCE

| Switching Method             | Conventional                    | V <sub>cm</sub> -Based                  |  |  |  |  |

|------------------------------|---------------------------------|-----------------------------------------|--|--|--|--|

| Technology                   | 90-nm CMOS                      | 90-nm CMOS                              |  |  |  |  |

| Resolution                   | 10-b                            | 10-b                                    |  |  |  |  |

| Sampling Rate                | 65-MS/s                         | 100-MS/s                                |  |  |  |  |

| Supply Voltage               | 1.2 V                           | 1.2 V                                   |  |  |  |  |

| Full Scale Analog Input      | 1.2V <sub>PP</sub> differential | 1.2 <i>V</i> <sub>PP</sub> differential |  |  |  |  |

| SNDR                         | 54.7 dB                         | 56.6 dB                                 |  |  |  |  |

| SFDR                         | 66 dB                           | 71 dB                                   |  |  |  |  |

| ENOB                         | 8.8-b                           | 9.1-b                                   |  |  |  |  |

| DNL                          | + 3/-1 LSB                      | + 0.79/- 0.27<br>LSB                    |  |  |  |  |

| INL                          | + 2.8/–1.6 LSB                  | + 0.86/- 0.78<br>LSB                    |  |  |  |  |

| DNL after Cal.               | + 0.9/-0.7 LSB                  | N/A                                     |  |  |  |  |

| INL after Cal.               | + 1/-1.1 LSB                    | N/A                                     |  |  |  |  |

| Power Consumption            |                                 |                                         |  |  |  |  |

| Sampling&DAC                 | 1.7 mW                          | 600\$\muW\$                             |  |  |  |  |

| Comparator                   | 3.3 mW                          | 800\$\muW\$                             |  |  |  |  |

| CLK Gen & SA Log             | 3.2 mW                          | 1.6 mW                                  |  |  |  |  |

| Total Power                  | 8.2 mW                          | 3 mW                                    |  |  |  |  |

| $FOM = Power/2^{ENOB}_{*fs}$ | 280 fJ/conv-step                | 55 fJ/conv-step                         |  |  |  |  |

Fig. 13. Measured INL and DNL of 10-b SAR ADC with conventional switching after calibration.

600

200

800

1000

is not a dominant factor in this design and the proposed digital calibration technique is applied to correct all the large nonlinearity codes. The calibrated DNL and INL results are presented in Fig. 13, where the large DNL and INL can be significantly reduced from 3 to 0.9 LSB and from 2.8 to 1.1 LSB, respectively. The SNDR drops by 0.5 dB upon the calibration. For the second SAR ADC, due to the advantages of  $V_{\rm cm}$ -based switching, no missing codes are presented implying that calibration is not necessary.

The measured performances of the two prototype SAR ADCs are summarized in Table II. The second

|                                                     | [2] ISSCC'08 | [3] VLSI'09 | [6] ISSCC'08 | [9] ISSCC'09 | This paper [24] JSSC'10 |

|-----------------------------------------------------|--------------|-------------|--------------|--------------|-------------------------|

| Architecture                                        | SAR          | SAR         | Pipelined    | Pipelined    | SAR                     |

| Technology (nm)                                     | 90           | 130         | 65           | 180          | 90                      |

| Resolution (bit)                                    | 9            | 10          | 10           | 10           | 10                      |

| Sampling rate (MS/s)                                | 40           | 50          | 100          | 50           | 100                     |

| Supply voltage (V)                                  | 1            | 1.2         | 1.2          | 1.8          | 1.2                     |

| SNDR (dB)                                           | 53.3         | 52.8        | 59           | 58.2         | 56.6                    |

| ENOB (bit)                                          | 8.6          | 8.5         | 9.5          | 9.4          | 9.1                     |

| DNL (LSB)                                           | + 0.7/-0.45  | + 0.88/-1   | + 0.1/-0.1   | N/A          | + 0.79/-0.27            |

| INL (LSB)                                           | + 0.56/-0.65 | + 2.2/-2.09 | + 0.2/-0.2   | + 0.7/-0.8   | + 0.86/-0.78            |

| Power (mW)                                          | 0.82         | 0.92        | 4.5          | 9.9          | 3                       |

| FOM = Power/2 <sup>ENOB</sup> *fs<br>(fJ/conv-step) | 54           | 52          | 62           | 300          | 55                      |

TABLE III

ISOTHERMAL SOLIDIFICATION REACTION RATE CONSTANTS ESTIMATED USING DSC DATA

design consumes 5.2 mW lower power than the first, of which 2.7 mW is the benefit from the  $V_{\rm cm}$ -based switching due to the reduction of switching power as well as the digital power from switching buffers. Another 2.5 mW of power reduction is due to the utilization of the dynamic comparator. Considering all the power benefits, the figure-of-merit (FoM) of the second design is improved from 280 fJ/conv-step to 55 fJ/conv-step. Table III benchmarks the prototype  $V_{\rm cm}$ -based SAR ADC (Fig. 9) with state-of-the-art ADCs. The design achieves competitive FoM for high-speed implementation.

### VII. CONCLUSION

Two 1.2 V 10-b SAR ADCs operating at tens of MS/s with conventional and  $V_{\rm cm}$ -based switching were presented. The linearity behaviors of the DACs switching and structure were analyzed and verified by both simulated and measured results. The  $V_{\rm cm}$ -based switching technique provides superior conversion linearity when compared with the conventional method because of its array's capacitors correlation during each bit cycling. The proposed code-randomized calibration can eliminate the large DNL and INL errors in the conventional switching. Measured results demonstrated that both higher speed and lower power is achieved by using  $V_{\rm cm}$ -based switching.

#### **APPENDIX**

## A. Sensitivity to Supply Noise

Using supply as a reference, removes not only the static power required in the resistive ladder and high-speed voltage buffer, but also their noise contribution. However, the package bonding inductor will generate switching noise with undesired ringing effect. In modern SoC design, the analog circuitry will be normally biased by a dedicated linear voltage regulator or LDO to isolate the large system digital noise. Commercial low-noise voltage regulator products achieve around several tens of  $\mu V$  RMS within a bandwidth of hundreds of KHz [30]. The proper placement of the decoupling capacitor can effectively attenuate the high-frequency noise. Therefore, the

inductive switching noise due to the current transient of the DAC becomes the critical and dominating contribution for the total reference noise. Thus, it is necessary to analyze the reference safety margin to guarantee the expected conversion accuracy.

The differential DAC for conventional and  $V_{\rm cm}$ -based switching with the simplified power networks are shown in Fig. 14. In  $V_{\rm cm}$ -based switching after (n-1) bit cycling, the DACs will finally settle to a value for LSBs decision. The differential DAC output is quite sensitive to supply variations, especially in the most critical case where the bottom plates of all the DAC capacitors (on the signal side) are connected to  $V_{\rm DD}$ . Since the operation is differential, considering one of the corresponding cases: all bits in  $V_{\rm op1}$  are "1" and all bits in  $V_{\rm on1}$  are "0," the differential output  $V_{\rm out}$  of the DACs can be represented as

$$V_{\text{out}} = V_{\text{op1}} - V_{\text{on1}}$$

$$= \left[ \frac{2^{n-1} - 1}{2^{n-1}} (V_{\text{DD}} + \Delta V) + \frac{1}{2^{n-1}} V_{\text{cm}} \right] - \frac{1}{2^{n-1}} V_{\text{cm}}$$

(24)

where  $\Delta V$  is the variation of the supply. Equation (24) is independent of  $V_{\rm cm}$ , since the differential operation cancels the relative terms. Consequently, the voltage error  $V_{\rm err}$  is obtained as

$$V_{\text{err}} = \frac{2^{n-1} - 1}{2^{n-1}} \Delta V \approx \Delta V. \tag{25}$$

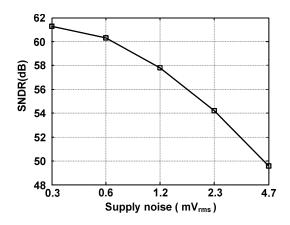

It requires that the error term  $|\Delta V|$  due to the supply-noise needs to be suppressed within 1/4 LSB (LSB = 1/2  $^nV_{\rm FS}$  = 1/2  $^{n-1}$   $V_{\rm DD}$ ). Then, leading to

$$\frac{|\Delta V|}{V_{\rm DD}} < \frac{1}{2^{n+1}}.\tag{26}$$

For 10-b accuracy, the supply variation needs to be suppressed within  $\pm$  0.049% of the full supply rail. It means that the supply ripple  $<\pm$  588  $\mu$ V for a 1.2 V supply. The supply ripple due to the switching effect is not problematic for a low speed SAR, since the DAC settling time is large enough. However, in high-speed designs, the request becomes

Fig. 14. Simplified supply network and differential DACs to perform  $V_{\text{cm}}$ -based and conventional switching.

Fig. 15. Behavioral simulation of SNDR versus the supply noise in a 10-b SAR ADC (10-b split DAC is used with a unit capacitance of 50 fF).

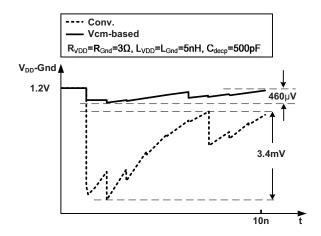

quite stringent. The design of a 10-b SAR running at 100 MS/s involves an overall time, available to determine each bit, which is <1 ns, including the time for comparison, SR logic delay, and DAC settling. A behavioral simulation shows that the conversion sensitivity to supply variation of a 10-b 100 MS/s SAR ADC is within  $\pm$  600  $\mu$ V, as illustrated in Fig. 15. According to the switching sequences of the binary-searched algorithm, the most critical transition happens at the charging of the largest capacitor. Since the  $V_{\rm cm}$ -based switching charges 75% less capacitance, simultaneously, when compared with the conventional switching, it can effectively reduce the under-shoot of the supply or reference buffer (when used). The supply waveforms of conventional and  $V_{\rm cm}$ -based methods with a switching frequency of 1 GHz are illustrated in Fig. 16 (Conventional and the  $V_{\rm cm}$ -based switching are

Fig. 16. Supply waveform of performing the conventional and  $V_{\rm cm}$ -based switching in a 10 b SAR ADC with the unit capacitance of 50 fF.

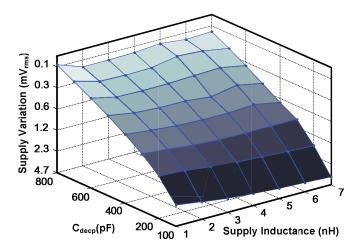

Fig. 17. Simulated supply variations versus sweeping of  $C_P$  and supply inductance in a 10 b  $V_{\rm cm}$ -based SAR ADC (9-b split DAC is used with a unit capacitance of 50 fF).

applied to a 10-b and 9-b split DAC with a unit capacitance of 50 fF).

The inductive ringing effect can be well suppressed by minimizing the bonding inductance, e.g., multiple bonding, adding damping resistor, and on-chip decoupling capacitor  $C_{\text{decp}}$ . Fig. 17 presents a plot of supply variation versus the sweeping of  $C_{\text{decp}}$  and bonding inductance in a 10 b  $V_{\text{cm}}$ -based SAR. It can be deduced that to achieve 10-b accuracy, with 2-5 nH bonding inductance, it would be necessary to have a decoupling capacitor with an approximate value of 500 pF, to suppress the switching reference noise. This value penalizes the die area, e.g., using typical pMOS as the decoupling capacitor with W  $\times$  L equal to 5  $\times$  5  $\mu$ m, the area for 500 pF would be close to 0.04 mm<sup>2</sup>. On the other hand, some SA searching algorithm like the nonbinary conversion [27] that relaxes the settling accuracy requirement during large switch transients would be the effective approach to overcome this problem.

## ACKNOWLEDGMENT

The authors would like to express their sincere appreciation to H. Venkatesan for the language editing and proofreading.

#### REFERENCES

- [1] J. Craninckx and G. V. Plas, "A 65 fJ/conversion-step 0-to-50 MS/s 0-to-0.7 mW 9b charge-sharing SAR ADC in 90 nm digital CMOS," in *IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2007, pp. 246–247.

- [2] V. Giannini, P. Nuzzo, V. Chironi, A. Baschirotto, G. Van der Plas, and J. Craninckx, "An 820 μW 9b 40 MS/s noise-tolerant dynamic-SAR ADC in 90 nm digital CMOS," in *IEEE Int. Solid-State Circuits Conf.*, *Dig. Tech. Papers*, Feb. 2008, pp. 238–610.

- [3] C. C. Liu, S.-J. Chang, G.-Y. Huang, and Y.-Z. Lin, "A 0.92 mW 10-bit 50-MS/s SAR ADC in 0.13 μm CMOS process," in Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2009, pp. 236–237.

- [4] P. Harpe, Z. Cui, W. Xiaoyan, G. Dolmans, and H. de Groot, "A 30 fJ/conversion-step 8b 0-to-10 MS/s asynchronous SAR ADC in 90 nm CMOS," in *IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2010, pp. 388–389.

- [5] M. Boulemnakher, E. Andre, J. Roux, and F. Paillardet, "A 1.2V 4.5 mW 10b 100 MS/s pipeline ADC," in *IEEE Int. Solid-State Circuits Conf.*, Dig. Tech. Papers, Feb. 2008, pp. 250–251.

- [6] S. T. Ryu, B. S. Song, and K. Bacrania, "A 10b 50 MS/s opamp-sharing pipeline A/D with current-reuse OTAs," *IEEE J. Solid-State Circuits*, vol. 42, no. 3, pp. 475–485, Mar. 2007.

- [7] K. Chandrashekar and B. Bakkaloglu, "A 1.8-V 22-mW 10-bit 30MS/s pipelined CMOS ADC for low-power subsampling applications," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 19, no. 2, pp. 1610–1616, Sep. 2011.

- [8] I. Ahmed, J. Mulder, and D. A. Johns, "A 50 MS/s 9.9 mW pipeline ADC with 58dB SNDR in 0.18 μm CMOS using capacitive charge-pumps," in *IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2009, pp. 164–165.

- [9] J. Hu, N. Dolev, and B. Murmann, "A 9.4-bit, 50-MS/s, 1.44-mW pipelined ADC using dynamic residue amplification," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2008, pp. 216–217.

- [10] O. A. Adeniran, A. Demosthenous, C. Clifton, S. Atungsiri, and R. Soin, "A CMOS low-power ADC for DVB-T and DVB-H systems," in *Proc. IEEE Int. Symp. Circuits Syst.*, vol. 1. May 2004, pp. 209–212.

- [11] U.-F. Chio, H.-G. Wei, Z. Yan, S. Sai-Weng, U. Seng-Pan, R. P. Martins, and F. Maloberti, "Design and experimental verification of a power effective Flash-SAR subranging ADC," *IEEE Trans. Circuits Syst. II*, *Exp. Briefs*, vol. 57, no. 8, pp. 607–611, Aug. 2010.

- [12] Y. Zhu, U.-F. Chio, H.-G. Wei, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "A power-efficient capacitor structure for high-speed charge recycling SAR ADCs," in *Proc. IEEE Int. Conf. Electron. Circuits Syst.*, Aug.—Sep. 2008, pp. 642–645.

- [13] Z. Cao, S. Yan, and Y. Li, "A 32 mW 1.25 GS/s 6b 2b/step SAR ADC in 0.13 μm CMOS," in *Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 542–543, Feb. 2008.

- [14] M. Saberi, R. Lotfi, K. Mafinezhad, and W. A. Serdijn, "Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation ADCs," *IEEE Trans. Circuit Syst. I, Regular Papers*, vol. 58, no. 8, pp. 1736–1748, Aug. 2011.

- [15] Y.-K. Cho, Y.-D. Jeon, J.-W. Nam, and J.-K. Kwon, "A 9-bit 80 MS/s successive approximation register analog-to-digital converter with a capacitor reduction technique," *IEEE Trans. Circuit Syst. II, Exp. Briefs*, vol. 57, no. 7, pp. 502–506, Jul. 2010.

- [16] M. S. W. Chen and R. W. Brodersen, "A 6b 600 MS/s 5.3-mW asynchronous ADC in 0.13-μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2006, pp. 574–575.

- [17] Y. Chen, S. Tsukamoto, and T. Kuroda, "A 9b 100 MS/s 1.46 mW SAR ADC in 65 nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Nov. 2009, pp. 145–148.

- [18] A. Agnes, E. Bonizzoni, P. Malcovati, and F. Maloberti, "A 9.4-ENOB 1V 3.8μW 100 kS/s SAR ADC with time-domain comparator," in *Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2008, pp. 246–247.

- [19] Y. F. Chen, X. Zhu, H. Tamura, M. Kibune, Y. Tomita, T. Hamada, M. Yoshioka, K. Ishikawa, T. Takayama, J. Ogawa, S. Tsukamoto, and T. Kuroda, "Split capacitor DAC mismatch calibration in successive approximation ADC," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2009, pp. 279–482.

- [20] M. Yoshioka, K. Ishikawa, T. Takayama, and S. Tsukamoto, "10b 50 MS/s 820 μW SAR ADC with on-chip digital calibration," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2010, pp. 384–385.

- [21] Y. Zhu, C.-H. Chan, U.-F. Chio, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "A voltage feedback charge compensation technique for split DAC architecture in SAR ADCs," in *Proc. IEEE Int. Symp. Circuits* Syst., May 2010, pp. 4061–4064.

- [22] S. Wong, Y. Zhu, C.-H. Chan, U.-F. Chio, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "Parasitic calibration by two-step ratio approaching technique for split capacitor array SAR ADCs," in *Proc. IEEE SoC Design Conf. Int.*, Nov. 2009, pp. 333–336.

- [23] B. P. Ginsburg and A. P. Chandrakasan, "500-MS/s 5-bit ADC in 65-nm CMOS with split capacitor array DAC," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 739–747, Apr. 2007.

- [24] Y. Zhu, C. H. Chan, U-F. Chio, S.W. Sin, U. Seng-Pan, R. P. Martins, and F. Maloberti, "A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 6, pp. 1111–1121, Jun. 2010

- [25] B. P. Ginsburg and A. P. Chandrakasan, "An energy-efficient charge recycling approach for a SAR converter with capacitive DAC," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2005, pp. 184–187.

- [26] U.-F. Chio, H.-G. Wei, Y. Zhu, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "A self-timing switch-driving register by precharge-evaluate logic for high-speed SAR ADCs," in *Proc. IEEE Asia Pacific Conf. Circuits Syst.*, Dec. 2008, pp. 1164–1167.

- [27] F. Kuttner, "A 1.2-V 10-b 20-Msample/s nonbinary successive approximation ADC in 0.13-μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2002, pp. 176–177.

- [28] M. Gustavsson, J. J. Wikner, and N. Tan, CMOS Data Converters for Communications, Norwell, MA, USA: Kluwer, 2000.

- [29] Y. Zhu, U.-F. Chio, H.-G. Wei, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "Linearity analysis on a series-split capacitor array for high-speed SAR ADCs," in *Proc. IEEE Midwest Symp. Circuits Syst.*, Aug. 2008, pp. 922–925.

- [30] Datasheet of Low Dropout Linear Regulator (2012). Standard ADP1752/ADP1753.

**Yan Zhu** (S'10–M'12) received the B.Sc. degree in electrical engineering and automation from Shanghai University, Shanghai, China, in 2006, and the M.Sc. and Ph.D. degrees in electrical and electronics engineering from the University of Macau Macao, China, in 2009 and 2011, respectively.

She is currently a Post-Doctoral Researcher with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macao, China. Her current research interests include low-power and wideband high-speed Nyquist A/D converters as well as digitally assisted data converter designs.

**Chi-Hang Chan** (S'12) received the B.Sc. degree from the University of Washington, Seattle, WA, USA, and the M.Sc. degree from the University of Macau, Macao, China, in 2012, where he is currently pursuing the Ph.D. degree.

He was an intern in Synopsys-Chipidea Microelectronics, Macau, during his undergraduate studies. His current research interests include gigahertz-range ADCs with low and moderate resolution, comparator, dynamic circuit design, and mixed-signal layout consideration.

**U-Fat Chio** received the B.Sc. degree in electrical engineering and the M.Sc. degree in communications engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2002 and 2004, respectively, and the Ph.D. degree from the University of Macau, Macao, China, in 2012.

He was with Den MOS Technology Inc., Hsinchu, Taiwan, from 2004 to 2005. He is currently a Post-Doctoral Fellow with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau. His current research interests include high-speed analog-to-digital converters and power management circuit designs.

Sai-Weng Sin (S'98–M'06) received the B.Sc., M.Sc., and Ph.D. degrees (with highest honor) in electrical and electronics engineering from the University of Macau, Macao, China, in 2001, 2003, and 2008, respectively.

He is currently an Assistant Professor with the Faculty of Science and Technology, University of Macau, Macao, China, and is the Coordinator of the Data Conversion and Signal Processing (DCSP) Research Line in State-Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau. He has authored one book, entitled Generalized Low-Voltage Circuit Techniques for Very High-Speed Time-Interleaved Analog-to-Digital Converters (Springer) and over 70 technical journals and conference papers in the field of high-performance data converters and analog mixed-signal integrated circuits.

Dr. Sin has been a member of the Technical Program Committee of IEEE Sensors 2011 and IEEE RFIT 2011–2012 Conference, Review Committee Member of Prime Asia 2009 Conference, Technical Program, and Organization Committee of the 2004 IEEJ AVLSI Workshop, as well as the Special Session Co-Chair and Technical Program Committee Member of 2008 IEEE APCCAS Conference. He is currently the Secretary of the IEEE Solid-State Circuit Society (SSCS) Macau Chapter and IEEE Macau CAS/COM Joint Chapter. He was the co-recipient of the 2011 ISSCC Silk Road Award, Student Design Contest winner in A-SSCC 2011 and the 2011 State Science and Technology Progress Award (second-class), China.

**Seng-Pan U** (S'94–M'00–SM'05) received the B.Sc. and M.Sc. degrees in 1991 and 1997, respectively, and the joint Ph.D. degree (with highest honor) in high-speed analog IC design from the University of Macau, Macao, China, the Instituto Superior Técnico, Universidade Técnica de Lisboa, Lisbon, Portugal, (IST/UTL) in 2002.

He has been with the Department of Electrical and Electronic Engineering, Faculty of Science and Technology (FST), University of Macau, since 1994, where he is currently a Professor and Deputy Director of State-Key Laboratory of Analog & Mixed-Signal VLSI of UM. From 1999 to 2001, he was also on leave to the Integrated CAS Group, Center of Microsystems, IST/UTL, as a Visiting Research Fellow. In 2001, he co-founded the Chipidea Microelectronics (Macau), Ltd., Macau, and was the Engineering Director and since 2003 the corporate Vice-President of IP Operations Asia Pacific and site General Manager of the company for devoting in advanced analog and mixed-signal Semiconductor IP (SIP) product development. Chipidea Group was acquired in May 2009 by Synopsys Inc. (NASDAQ: SNPS), the world leading EDA and IP provider, he is currently the corporate Senior Analog Design Manager and Site General Manager. He holds five U.S. patents and has co-authored Design of Very High-Frequency Multirate SC Circuits—Extending the Boundaries of CMOS AFE Filtering, Analog-Baseband Architectures and Circuits for Multistandard and Low-Voltage Wireless Transceivers, and Generalized Low-Voltage Circuit Techniques for Very High-Speed TI ADCs (Springer), and the foremost one was selected in 2007 by China Science Press for republication in The Overseas Electronics & Information Book Excellence Series.

Dr. U was the recipient of various scholarship and R&D grants and published more than 120 scientific papers in IEEE/IET journal and conferences. He has received 20\_ research & academic/teaching awards and is also the advisor for 20 various international student paper award recipients. e.g., ISSCC Silk-Road Award, IEEE DAC/ISSCC Student Design Contest, A-SSCC Student Design Contest, ISCAS, MWSCAS, and IEEE PRIME. He also received, at the first time from Macau, the Scientific and Technological Innovation Award of Ho Leung Ho Lee Foundation in 2010, and The State Scientific and Technological Progress Award in 2011. In recognition of his contribution in high-technology research & industrial development in Macau, he was awarded by Macau SAR government the Honorary Title of Value in 2010. He is currently the Industrial Relationship Officer of IEEE Macau Section, the Chairman of the IEEE Macau CAS/COMM chapter, and the founding Chairman of the IEEE Macau SSC Chapter. He has been with technical review committee of various international scientific journals and conferences for many years, e.g., JSSC, TCAS, IEICE, and ISCAS. He was the Chairman of the local organization committee of IEEJ AVLSIWS'04, the Technical Program co-Chair of IEEE APCCAS'08, ICICS'09 and PRIMEAsia'11. He is currently the Technical Program Committee of RFIT, VLSI-DAT, and A-SSCC.

**Rui Paulo Martins** (M'88-SM'99-F'08) was born on April 30, 1957. He received the B.Sc, M.Sc. and Ph.D. degrees, as well as the Habilitation for Full-Professor, in electrical engineering and computers from Instituto Superior Técnico (IST), TU of Lisbon, Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

He has been with the Department of Electrical and Computer Engineering (DECE)/IST, TU of Lisbon, since October 1980. Since 1992, he has been on leave from IST, TU of Lisbon, and is also with the Department of Electrical and Computer Engineering, Faculty of Science and Technology (FST), University of Macau (UM), Macao, China, where he has been a Full Professor since 1998. At FST, he was the Dean of the Faculty from 1994 to 1997 and he has been Vice-Rector of the University of Macau since 1997. From September 2008, after the reform of the UM Charter, he was nominated after open international recruitment as Vice-Rector (Research) until August 31, 2013. Within the scope of his teaching and research activities, he has taught 21 bachelor and master courses and has supervised (or cosupervised) 25 theses, Ph.D. (11) and Masters (14). He has published 12 books, coauthoring five and coediting seven, plus five book chapters, 230 refereed papers, in scientific journals and conference proceedings, as well as other 70 academic works, in a total of 317 publications. He has coauthored four U.S. Patents (two issued in 2009 and two in 2011) and with another six pending. He has created the Analog and Mixed-Signal VLSI Research Laboratory of UM, elevated in January 2011 to State Key Lab of China (the 1st in Engineering in Macao), being its Founding Director. He is the financial manager, recognized by the European Union, of a Jean Monnet Chair in "EULaw-Facing the Constitution and Governance Challenges in the Era of Globalization", unique in the universities from HK & Macao, for the period 2007 to 2012.

Prof. Rui Martins was the Founding Chairman of the IEEE Macau Section from 2003 to 2005 and of the IEEE Macau Joint-Chapter on Circuits And Systems (CAS)/Communications (COM) from 2005 to 2008 (2009 World Chapter of the Year of the IEEE Circuits nd Systems (CAS) Society). He was the General Chair of the 2008 IEEE Asia-Pacific Conference on Circuits And Systems- APCCAS'2008, and was the Vice-President for the Region 10 (Asia, Australia, the Pacific) of the IEEE CAS Society for the period 2009 to 2011. He was elected recently to the position of Vice-President (World) Regional Activities and Membership also of the IEEE CAS Society for the period 2012 to 2013. He has been an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS since 2010. He was the recipient of two government decorations: the Medal of Professional Merit from Macao Government (Portuguese Administration) in 1999, and the Honorary Title of Value from Macao SAR Government (Chinese Administration) in 2001. In July 2010 he was unanimously elected, as a Corresponding Member of the Portuguese Academy of Sciences (in Lisbon), being the only Portuguese academician living in Asia.

**Franco Maloberti** (A'84-SM'97-F'96) received the Laurea degree in physics (*summa cum laude*) from the University of Parma, Parma, Italy, in 1968, and the Dr. Honoris Causa degree in electronics from Inaoe, Puebla, Mexico, in 1996. He was a Visiting Professor with ETH-PEL, Zurich, in 1993 and with EPFL-LEG, Lausanne, in 2004.

He was a Professor of Microelectronics and Head of the Micro Integrated Systems Group University of Pavia, Pavia, Italy, TI/J.Kilby Analog Engineering Chair Professor with the Texas A&M University and the Distinguished Microelectronic Chair Professor with University of Texas at Dallas. Currently, he is a Professor with the University of Pavia, Pavia, Italy, and Honorary Professor with the University of Macau, Macao, China. He has written more than 450 published papers, five books, and holds 30 patents. He has been responsible for many research programs including ten ESPRIT projects and served the European Commission in many European Initiatives. He served the Academy of Finland on the assessment of electronic research. He served the National Research Council of Portugal for the research activity assessment of Portuguese Universities. He is the Chairman of the Academic Committee of the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macao, China.

Prof. Maloberti was VP Region 8 of the IEEE Circuits and Systems (CAS) Society (1995-1997), Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, President of the IEEE Sensor Council (2002-2003), an IEEE CAS BoG member (2003-2005), and VP Publications for IEEE CAS (2007-2008). He was a Distinguished Lecturer for the IEEE Solid-State Circuits Society (2009-2010) and presently is a Distinguished Lecturer for the IEEE CAS Society. He received the 1999 IEEE CAS Society Meritorious Service Award, the 2000 CAS Society Golden Jubilee Medal, and the IEEE Millenium Medal. He received the 1996 IEE Fleming Premium, the ESSCIRC 2007 Best Paper Award and the IEEE Workshop 2007, and 2010 Best Paper Award. He is IEEE Fellow. In 1992, he was a recipient of the XII Pedriali Prize for his technical and scientific contributions to national industrial production.