# A 0.83- $\mu$ W QRS Detection Processor Using Quadratic Spline Wavelet Transform for Wireless ECG Acquisition in 0.35- $\mu$ m CMOS

Chio-In Ieong, Pui-In Mak, Senior Member, IEEE, Chi-Pang Lam, Cheng Dong, Mang-I Vai, Senior Member, IEEE, Peng-Un Mak, Senior Member, IEEE, Sio-Hang Pun, Feng Wan, and Rui P. Martins, Fellow, IEEE

Abstract-Healthcare electronics count on the effectiveness of the on-patient signal preprocessing unit to moderate the wireless data transfer for better power efficiency. In order to reduce the system power in long-time ECG acquisition, this work describes an on-patient QRS detection processor for arrhythmia monitoring. It extracts the concerned ECG part, i.e., the RR-interval between the QRS complex for evaluating the heart rate variability. The processor is structured by a scale-3 quadratic spline wavelet transform followed by a maxima modulus recognition stage. The former is implemented via a symmetric FIR filter, whereas the latter includes a number of feature extraction steps: zero-crossing detection, peak (zero-derivative) detection, threshold adjustment and two finite state machines for executing the decision rules. Fabricated in 0.35-µm CMOS the 300-Hz processor draws only 0.83  $\mu$ W, which is favorably comparable with the prior arts. In the system tests, the input data is placed via an on-chip 10-bit SAR analog-to-digital converter, while the output data is emitted via an off-the-shelf wireless transmitter (TI CC2500) that is configurable by the processor for different data transmission modes: 1) QRS detection result, 2) raw ECG data or 3) both. Validated with all recordings from the MIT-BIH arrhythmia database, 99.31% sensitivity and 99.70% predictivity are achieved. Mode 1 with solely the result of QRS detection exhibits 6 × reduction of system power over modes 2 and 3.

*Index Terms*—QRS detection, quadratic spline wavelet transform, wavelet transform, wearable electrocardiograph (ECG) device, wireless ECG monitoring.

## I. INTRODUCTION

W IRELESS electrocardiogram (ECG) acquisition electronics has emerged as a comfortable low-cost technology for continuous cardiac monitoring. In order to release the patients from bulky devices and heavy wire connection, the on-patient front-end unit must be miniaturized in size and consume very low power. There are essentially three functional blocks: 1) an analog front-end for amplification and filtering, 2) an analog-to-digital converter (ADC) for digitization, and 3)

Manuscript received September 23, 2011; revised December 04, 2011; accepted February 03, 2012. Date of publication April 05, 2012; date of current version January 14, 2013. This paper was recommended by Associate Editor P. Chiang.

The authors are with the Department of Electrical and Computer Engineering, Faculty of Science and Technology, University of Macau, Taipa, Macao 999078, China (e-mail: ciieong@umac.mo; pimak@umac.mo; ppnathan@gmail.com; donc@163.com; fstmiv@umac.mo; fstpum@umac.mo; lodgepun@umac.mo; fwan@umac.mo; rmartins@umac.mo).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TBCAS.2012.2188798

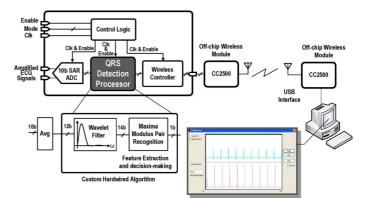

Fig. 1. QRS detection processor for a wireless ECG acquisition system.

a wireless transmitter for delivering the data to the back-end unit. Among them, as evidenced in other wireless biopotential acquisition systems [1], [2], the wireless transmitter dominates the system power. One effective way to save the wireless energy in Electroencephalography (EEG) seizure detection [1] is to locally compute the frequency-band energies before delivering the data, leading to  $14 \times$  system power saving comparing to full data transmission. For the wireless capsule endoscope reported in [2], local image compression leads to  $2 \times$  system power reduction.

For cardiac monitoring, the complete ECG data is normally a surplus in healthcare level. For instance, long-time arrhythmia monitoring is to detect the occurrence of arrhythmia and store an interval of the abnormal ECG, avoiding emitting and storing large amount of data [3]. In fact, just the RR-interval between the QRS complex is sufficed to accurately compute the heart rate variability (HRV) [4], [5]. In this respect, local signal preprocessing becomes a prospective way to avoid transmitting the redundant data. This paper describes a customized digital signal processor for system power reduction in a wireless ECG acquisition system (Fig. 1). The key attributes of the processor are the Quadratic Spline Wavelet Transform (QSWT), feature extraction and decision-making stages to optimize the detection accuracy of the QRS complex. A 10-bit SAR ADC (over-sampled by 4 to realize an effective resolution of 12 bits) and a wireless controller are co-integrated on chip to allow real-time verification. The wireless module is an off-the-shelf device similar to that in [1], which is managed by the proposed processor to transmit the data under different formats (i.e., the QRS detection result, the raw ECG data or both). With this flexibility, the full ECG data is also obtainable on demand, and the efficiency of the processor can be evaluated by comparing the power dissipation in each mode. The back-end of the system is a PC terminal that displays the digitized ECG signal, QRS complex occurrence and heart rate in real time. The recorded ECG data can be stored for further analysis.

The fabricated 0.35- $\mu$ m CMOS processor with paralleland pipeline-intensive architecture minimizes the clock rate (300 Hz) for achieving a 300-Sa/s throughput, measuring a very low consumption of 0.83  $\mu$ W that compares much favorably with the available low-power processors; all still draw tens to hundreds of  $\mu$ W at their specified lowest clock rate of 1 MHz [6]–[9].

This paper is organized as follows: Section II introduces the QRS detection, discusses the ways of realization and briefly reviews the principles of wavelet transform (WT). Section III details the stage realization of the proposed QRS detection processor. The experimental results are reported in Section IV. The conclusions are drawn in Section V.

#### II. QRS DETECTION FOR ECG SIGNAL PROCESSING

In this section, the background of QRS detection is reviewed and its implementation method is discussed. The key principles and advantages of WT are briefly summarized.

## A. QRS Detection

ECG is the heart biopotential consisting of P, QRS complex, T and U waves. The QRS complex strongly reflects the activity of the heart during ventricular contraction. Due to its detectfriendly characteristic shape, it can be served as the basis for automated determination of heart rate, or further ECG analysis such as the HRV, which is a key indicator of an individual's cardiovascular system. Substantial research effort had been paid on QRS detection [10].

There are two factors making QRS detection challenging: 1) ECG signal is likely contaminated by much noise and artifacts, such as powerline interference, electrode contact noise, patient-electrode motion artifacts, Electromyography (EMG), baseline wandering, data collecting device noise, quantization noise and aliasing, etc. 2) The wide variation of QRS morphologies and rhythms, from abnormal ECGs and interpersonal variations [11], [12]. As a result, a QRS detector must be particularly robust over noise and disturbance.

QRS complex detection algorithms typically consist of a preprocessing stage and a decision stage. The former is mainly based on baseline wandering removal, high frequency noise removal and transform of ECG waveform to specific patterns. The decision stage is to apply decision rules for QRS detection. The sensitivity (Se) and predictivity (Pr) of common software-based QRS detection methods are summarized in Table I. Among them, the WT shows the highest detection accuracy to date. Furthermore, WT can be realized with filter banks [13] which are implementation-friendly with digital circuits. WT method is therefore selected as the basis for this research.

QRS detection can be realized differently. An analog circuit can be low power and compact, but suffering from performance variability and process dependence [14]. Although general-purpose processors can offer re-configurability and excellent

TABLE I SUMMARY OF QRS DETECTION METHODS

| Method                  | Se (%) | Pr (%) | Ref     |

|-------------------------|--------|--------|---------|

| Wavelet Transform       | 99.90  | 99.94  | [17]    |

| Band Pass Filter        | 99.69  | 99.77  | [3, 18] |

| Curve Length Transform  | 99.65  | 99.77  | [19]    |

| Filter Bank             | 99.59  | 99.56  | [20]    |

| Genetic Algorithm       | 99.60  | 99.51  | [21]    |

| Mathematical Morphology | 99.38  | 99.48  | [22]    |

accuracy, the power dissipation is still too high for long-time monitoring. As flexibility and efficiency are generally trade-off in processors, avoiding the unnecessary overheads (e.g., extra logic, memory, IO ports) [15], [16] should potentially yield the highest power efficiency. In this work, a tailor-made digital processor is proposed for QRS detection, which allows more design flexibility for performance enhancements.

## B. Wavelet Transform (WT)

WT is widely employed for singular point detection [17], [23]. It is also simple for digital circuit implementation as finite impulse response (FIR) filter structure can be employed for realization and the required number of gates and registers is normally small. The WT of a signal f(t) is defined as

$$W_s f(u) = \langle f, \psi_{u,s} \rangle = \int_{-\infty}^{+\infty} f(t) \frac{1}{\sqrt{s}} \psi^* \left(\frac{t-u}{s}\right) dt \quad (1)$$

where Wf means wavelet transform of signal f with mother wavelet  $\psi$  with translation u and dilation s [24]. Symbol \* denotes complex conjugate. Here s is a scale parameter often selected as the power of two,  $s = 2^j$  ( $j \in Z$ ), where Z denotes integer. This type of WT is called dyadic WT. The dyadic WT can be calculated with Mallat's algorithm as follows:

$$S_{2^{j}}f(n) = \sum_{k \in \mathbb{Z}} h_k S_{2^{j-1}}f(n-2^{j-1}k)$$

(2)

$$W_{2^{j}}f(n) = \sum_{k \in \mathbb{Z}} g_k S_{2^{j-1}} f(n-2^{j-1}k).$$

(3)

Thus the WT can be computed with FIR filters with coefficients  $\overline{h}_k$  and  $\overline{g}_k$  ( $\overline{h}_k = h_{-k}$  and  $\overline{g}_k = g_{-k}$ , together with down sampling recursively.

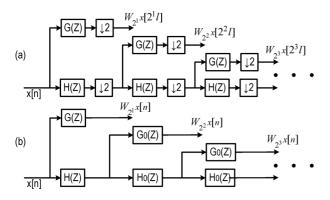

To provide approximate translation invariance which is important for detecting the temporal location of QRS complex, inserting zeros in the filter coefficients are performed instead of performing down sampling in WT. This is the "à trous" algorithm [25], [26] meaning zeros in the filter coefficients. Fig. 2 summarizes the differences of Mallat's and "à trous" algorithms.

## III. STAGE REALIZATION OF THE QRS DETECTION PROCESSOR

This section details the realization of each stage: QSWT, feature extraction and decision-making.

Fig. 2. (a) The Mallat's algorithm for WT. (b) "à trous" algorithm for WT. Here H(Z) and G(Z) mean the QSWT filters with coefficients shown in (5).  $H_0(Z)$  and  $G_0(Z)$  are the filters with coefficients inserted zeros.

## A. Quadratic Spline Wavelet Transform (QSWT)

We employ the QSWT with compact support, and one vanishing moment as the mother wavelet  $\psi(x)$ . It is a 1st derivative of the smooth function. The QSWT is introduced in [27] and applied to QRS detection in [17]. Currently this method keeps highest detection accuracy comparing the other methods. Its compact support characteristic enables the FIR filter to be implemented with fewer taps. The Fourier transform characterizing its frequency response is shown as follows:

$$\Psi(\omega) = i\omega \left[\frac{\left(\sin\frac{\omega}{4}\right)}{\frac{\omega}{4}}\right]^4.$$

(4)

The corresponding filter coefficients are

$$\overline{h}(x) = \begin{bmatrix} \frac{1}{8} & \frac{1}{8} & \frac{1}{8} & \frac{1}{8} \end{bmatrix}$$

$$\overline{g}(x) = \begin{bmatrix} -2 & 2 \end{bmatrix}.$$

(5)

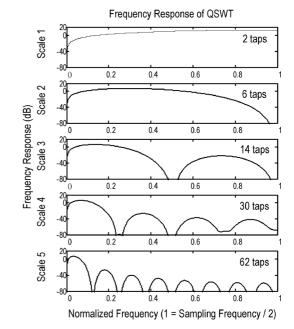

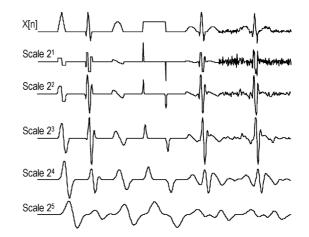

Fig. 3 shows the frequency responses of QSWT in one to five scales. The signal in various scales after QSWT comparing with the original ones is shown in Fig. 4. The output signal, which is called wavelet coefficients, is corresponding to the smoothed derivative of the input signal. One can read that the triangular waveform similar to R peak is transformed to modulus maxima pair (positive-maximum-negative-minimum pair). The zero-crossing point in modulus maxima pair corresponds to the R peak.

Note that the higher scale computation demands more filter taps and more power. After analysis, scale 3 of the QSWT is chosen for the ECG processing by considering the frequency distribution of the QRS complex, and filter tap number. The baseline wandering removal and 50/60 Hz notch filtering are expected to be provided in the analog front-end [28], [29] for power and area concerns. Besides the attenuation of baseline wandering of QSWT as shown in Fig. 3, further logic resource is not allocated in baseline wandering removal and 50/60 Hz notch filtering.

The input data type of QSWT is in a 12-bit 2's complement format. The bit width is compatible with [30], [31]. After the multiplication and addition computations, the data are truncated into a 14-bit 2's complement format by simulation optimization for power reduction.

Fig. 3. Frequency responses of QSWT scales.

Fig. 4. Various shapes and their QSWT coefficients.

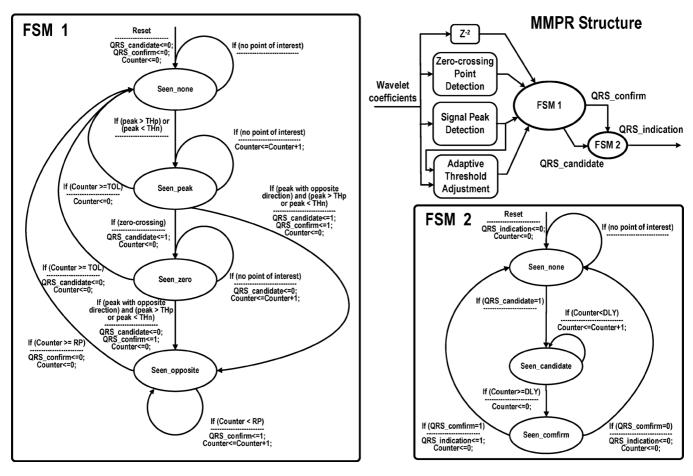

#### B. Modulus Maxima Pair Recognition Stage

The design of modulus maxima pair recognition (MMPR) stage is based on the principle of divide-and-conquer to solve the problem of recognizing the modulus maxima pair. As shown in Fig. 5 the MMPR structure, these works are attained by several sub-circuits for feature extraction and decision-making. The feature extraction is accomplished by zero-crossing detection, peak (zero-derivative) detection and threshold adjustment. The decision-making is realized by two finite state machines (FSM) for decision rule implementation. The features are extracted in parallel to minimize the clock rate of the circuits. The parallelism can further the power reduction since the circuit can operate slowly for the same computation, leaving much clock-delay margin for voltage supply reduction (i.e., power savings).

According to the information from the three sub-circuits, FSMs change state when finding a positive or negative peak, a zero crossing point and a peak with opposite direction to the previous peak, and output the markings of the temporal locations of QRS complexes.

Fig. 5. Modulus Maxima Pair Recognition (MMPR) module and the two corresponding FSM for realizing the decision rules. Here peak means the point with derivative equal to zero. RP is refractory period meaning the blanking period rejecting the coming detection of QRS complex. TOL meaning tolerance is the waiting period for resetting the FSM. DLY is a fixed waiting period for QRS indication output. What under the dashed line are the actions.

1) Zero-Crossing Detection: The zero-crossing detection circuit checks the 14-bit 2's complement formatted wavelet coefficient input, and outputs the 1-bit indication of QRS complex occurrence. If the input wavelet coefficient is zero, the zero-crossing detection circuit directly outputs the indication, specifying the zero point in input data. In another more common condition, if the neighboring two samples of data are with opposite signs, the indication of zero-crossing will be outputted when the latter sample is inputted to the circuit. The equations are shown as follows:

$$if (x[n] \leq 0)and(x[n+1] > 0) \Rightarrow ZC[x[], n] = 1$$

$$if (x[n] \geq 0)and(x[n+1] < 0) \Rightarrow ZC[x[], n] = 2$$

$$Others \Rightarrow ZC[x[], n] = 0 \quad (6)$$

where x is the input time series; n is the sample number; ZC represents the zero-crossing detection function.

2) Peak Detection: The peak detection circuit checks the 14-bit 2's complement formatted wavelet coefficient input, and outputs the 2-bit indication of the upward or downward peaks by detecting the zero-derivative points, which are the zero-crossing points of the first derivative of input wavelet coefficients. It employs a filter circuit with coefficients of  $\begin{bmatrix} 1 & -1 \end{bmatrix}$  and the zero-crossing detection circuit to realize this function. The equa-

tions that follow show where d approximates the derivative of input signal; ZC is now processing the time series d:

$$d[n] = x[n+1] - x[n]$$

if  $(ZC(d[], n) = 1) \Rightarrow Upward Peak$

if  $(ZC(d[], n) = 2) \Rightarrow Downward Peak.$  (7)

3) Threshold Adjustment: The threshold adjustment circuit classifies the peaks (zero-derivative points) of the input wavelet coefficients into peaks induced by noise and peaks induced by QRS complexes, and then stores the amplitudes of these peaks. The inputs of threshold adjustment circuit are the 14-bit 2's complement formatted wavelet coefficients and the 2-bit indication from peak detection circuit. The outputs are two threshold values in 14-bit 2's complement format, positive threshold and negative threshold. According to the amplitudes of recent classified peaks, the threshold adjustment circuit estimates the amplitude of noise signal and the amplitudes of modulus maxima which are induced by the QRS complexes. By multiplying empirical coefficients to estimated noise amplitude and signal amplitude, the thresholds are generated. The equations for threshold calculation follow:

$$if \ peak[n] \ge TH \Rightarrow Signal \ Peak$$

$$if \ peak[n] < TH \Rightarrow Noise \ Peak \tag{8}$$

$$ASPL = \frac{1}{M} \sum_{m=0}^{M-1} SignalPeak[n-m]$$

(9)

$$ANPL = \frac{1}{M} \sum_{m=0}^{M-1} NoisePeak[n-m]$$

(10)

$$TH = ANPL + \beta(ASPL - ANPL) \qquad (11)$$

where TH is the threshold output from the threshold adjustment circuit. Signal Peak is the point with derivative which equals to zero and is classified as induced by the QRS complex. Noise Peak means the point with derivative which equals to zero and is classified as induced by noise. Averaged Signal Peak Level (ASPL) is the running estimation of the signal peak (maxima) amplitude. Averaged Noise Peak Level (ANPL) is the running estimation of the noise amplitude.  $\beta$  is a percentage number. The variable M affects the speed of ASPL or ANPL in responding to the new SignalPeak or NoisePeak data. Here M is selected as 8 by simulation.

The calculation of positive and negative thresholds is done by two sets of these variables.

4) Finite State Machine (FSM): The decision-making is based on a temporal relationship of the aforementioned feature points. For preventing large data storage, two finite state machines are employed for decision-making, as shown in Fig. 5. They embody the decision rules in the state transition graph. FSM 1 is for the decision-making and FSM 2 is for marking the QRS complex position according to the signals from FSM 1. Four states are designed for representing the modulus maxima pair in FSM 1. The states follow.

| Seen_none     | is the starting state.                                                                    |

|---------------|-------------------------------------------------------------------------------------------|

| Seen_peak     | means that the FSM has already detected<br>a peak exceeded the threshold (valid<br>peak). |

| Seen_zero     | means that the FSM found the zero-crossing point after finding the valid peak.            |

| Seen_negative | means the FSM found a peak with opposite direction and exceeding the threshold.           |

The decision rules are:

*Classification Case 1:* If the Seen\_peak, Seen\_zero and Seen\_opposite states are passed, then the corresponding segment of signal is recognized as valid modulus maxima pair.

*Classification Case 2:* If the Seen\_peak and Seen\_opposite states are passed, the corresponding segment of signal is recognized as valid modulus maxima pair.

*Waiting Period:* If no valid peak or zero-crossing point encountered, the state machine would stay in the same state for a period of time, set as 0.07 s.

*Reset Condition:* If it stays in the same state for a period (0.07 s), or it is system startup, the state machine goes back to Seen\_none state. This rule is helpful for system stability.

*Refractory Blanking:* After the state machine enters the Seen\_opposite state, the state machine will stay in the same state in the coming 25 samples, and then it is directed to Seen none

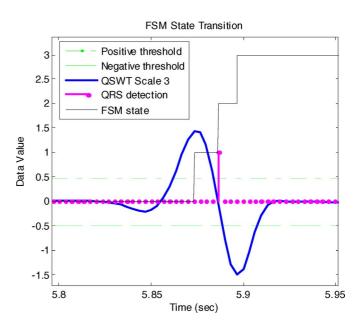

Fig. 6. State transitions (sampling rate = 300 Hz).

state. This is because there is a physiological refractory period of about 200 ms after a QRS complex, which is without the occurrence of QRS complex [3]. It is helpful to decrease the possibility of false detection.

Since the temporal location of zero-crossing point within modulus maxima pair corresponds to the temporal location of QRS complex, but the zero-crossing point is inside the modulus maximum pair, the zero-crossing points are considered as potential QRS complex candidates and temporarily marked before finally seeing the whole modulus maxima pair.

The detailed architectures of the two FSMs are shown in Fig. 5. The state transition and corresponding detection signals are shown in Fig. 6. Two QRS detection cases of ECG signals without and with baseline wondering from the MIT-BIH arrhythmia database [30] are shown in Figs. 7 and 8, respectively.

For example, when a detection cycle starts, both FSM 1 and FSM 2 are in Seen none states. These states keep until a peak with amplitude exceeding the positive or negative threshold according to the signals from Signal Peak Detection circuit and Adaptive Threshold Adjustment circuit. Then FSM 1 transits to Seen peak state and stays if no zero-crossing point is found, for a waiting period TOL counted by the counter. When a zerocrossing point is found according to Zero-crossing Detection circuit, FSM 1 transits to Seen-zero state and sets the QRS candidate register to 1 to inform FSM 2 that a potential QRS complex point is found. On the other hand, FSM 2 then transits from Seen none state to Seen candidate state and starts counting the time in this state. If FSM 1 sees a peak exceeding the thresholds with opposite direction to the previous found peak, it sets the QRS confirm register to 1 for confirming the validity of the potential QRS complex point. Then FSM 1 stays in Seen opposite state for a refractory period (RP) for rejecting the new detection. On the other hand, FSM 2 transits to Check confirm state after a fixed delay, then it will check the QRS confirm value and output the QRS indication value. Finally, FSM 1 and FSM 2 run back to Seen none states.

Fig. 7. Case 1: Corresponding signals for QRS detection.

Fig. 8. Case 2: Corresponding signals for QRS detection.

FSM 1 sets the QRS\_candidate signal to 1 when it enters the Seen zero state, and also set the QRS confirm signal to 1 within

the whole Seen\_opposite state. According to the QRS\_candidate and QRS\_confirm signals, FSM 2 can mark the QRS complexes with fixed delay.

## C. System Design

A 10-bit SAR ADC and a wireless controller are also incorporated in the design for testing the whole system in real time. The conversion range is given by the voltage references. The key performance metrics are:  $|INL_{typ}| = 0.9 \text{ LSB}$ , |INL| < 2 LSB,  $|DNL_{typ}| = 0.3 \text{ LSB}$ , |DNL| < 1 LSB. ENOB = 9.4 bits. The ADC oversamples the signal by a factor of 4 to re-produce an equivalent resolution of 12 bits. The clock frequencies of the ADC, QRS detection processor and system controller are 13.2 kHz, 300 Hz and 76.8 kHz respectively. Since the sampling rates of MIT-BIH Arrhythmia database and American Heart Association ECG database are 360 and 250 Hz respectively, the 300-Hz sampling rate within the region is justified [30], [31].

The input of the QRS detection processor is of 12-bit 2's complement format. The output is either a 1-bit indication of the QRS complexes or the raw ECG signal.

The wireless controller drives the off-chip TI CC2500 module [32]. Three transmission modes are offered: 1) the QRS detection result, 2) the ECG raw data, 3) both. In modes 2 and 3, 2 bytes are utilized per data packet, which includes one raw 12-bit data and one 1-bit QRS detection result and 3 control bits. In mode 1, we use one byte per data packet, which contains 3 control bits and five 1-bit QRS detection results. Therefore, the CC2500 transmits about  $10 \times less$  in mode 1 than in modes 2 and 3, lowering significantly the system power.

The specification of biopotential analog front-end can be found in [33], with programmable gain and signal filtering capability. The expected power consumption of it is 60  $\mu$ W or lower. Although baseline wandering removal is commonly entailed for signal preconditioning in QRS detection, it is suggested not to realize it digitally because: 1) the baseline wandering can be more power and area efficient when realized in the analog front-end; 2) the QSWT already has a highpass response to attenuate the low frequency noise; 3) baseline wandering removal consumes large amount of logic resource (area) and power in the digital domain as the computational cost of baseline wandering removal is usually large (i.e., the cut-off frequency of the filter must be very low comparing to sampling frequency). For instance, filtering the low frequency noise via multi-scale mathematical morphology has been tried in the layout synthesis, but demanding huge chip area.

The realization of the processor is also speed-optimized to avoid a high frequency clock. The whole processor operates in pipeline and parallel architecture for feature extraction. The clock rate is 300 Hz with 1 sample/clock cycle. This slow-andparallel technique lowers the logic delay requirement. A single 1.8-V supply is employed to allow reliable operation of all circuitry including the ADC in real-time measurements.

## **IV. EXPERIMENTAL RESULTS**

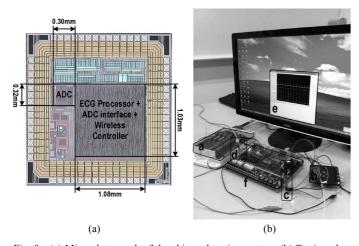

The processor (including the wireless controller) fabricated in 0.35- $\mu$ m CMOS occupies  $1.03 \times 1.08 \text{ mm}^2$ , whereas the ADC occupies  $0.25 \times 0.32 \text{ mm}^2$ . The entire IC was tested at a single

Fig. 9. (a) Microphotograph of the chip and testing system. (b) Testing platform of the chip. (a) NI Signal Acquisition/Generation Board for generating corresponding analog signal of MIT-BIH arrhythmia database. (b) The reported IC in a socket. (c) The off-chip RF module. (d) Wireless receiver. (e) Signal display user interface. (f) FPGA board for generating the clock for IC.

TABLE II

POWER CONSUMPTION (WITHOUT THE ACQUISITION ANALOG FRONT-END)

| V <sub>DD</sub> | Mode * | Power       |                 |                     |               |  |

|-----------------|--------|-------------|-----------------|---------------------|---------------|--|

|                 |        | ADC<br>(µW) | Digital<br>(µW) | Wireless TX<br>(mW) | Total<br>(mW) |  |

|                 | 1      | 2.36        | 0.83            | 1.57                | 1.58          |  |

| 1.8V            | 2      | 2.38        | 1.55            | 9.37                | 9.38          |  |

|                 | 3      | 2.66        | 1.57            | 9.37                | 9.38          |  |

\*Mode 1 stands for sending QRS detection result only. Mode 2 stands for sending raw ECG data. Mode 3 stands for sending both raw ECG data and QRS detection result.

1.8-V supply. Fig. 9 shows the chip microphotograph and the testing platform of the chip.

## A. Performances of the QRS Processor

Table II summarizes the power consumed by each block in the 3 data transmission modes. Since only the QRS complex occurrence is transmitted in Mode 1, it lowers effectively the system power by  $6 \times$ , verifying the feasibility of the proposed QRS detection processor. The wireless module TI CC2500 operates at 2.4 GHz with an output power of 0 dBm. In the system tests, the ECG signal is transmitted in a room at light-of-sight distance of 10 m. The Baud-rate is set to 250 kBaud and the package size is 12 bytes.

## B. Verification With MIT-BIH Arrhythmia Database

The MIT-BIH arrhythmia database [30] is employed to evaluate the detection accuracy of the processor in real time under wireless acquisition. It is with 48 recordings of ambulatory ECG signal from 47 subjects. The signals are with a 360-Hz sampling rate, an 11-bit resolution and a 10-mV amplitude range. The performance indices: Sensitivity (Se) and positive prediction (Pr) can be calculated with the equations given by

$$Se(\%) = \frac{TP}{TP + FN} \tag{12}$$

$$Pr(\%) = \frac{TP}{TP + FP} \tag{13}$$

TABLE III DETECTION RESULT WITH MIT-BIH DATABASE

| record | Total (beat) | FN  | FP  | Se (%) | Pr (%) |

|--------|--------------|-----|-----|--------|--------|

| 100    | 2265         | 0   | 1   | 100.00 | 99.96  |

| 101    | 1860         | 1   | 1   | 99.95  | 99.95  |

| 102    | 2180         | 0   | 0   | 100.00 | 100.00 |

| 103    | 2078         | 0   | 0   | 100.00 | 100.00 |

| 104    | 2222         | 6   | 24  | 99.73  | 98.93  |

| 105    | 2565         | 27  | 48  | 98.95  | 98.14  |

| 106    | 2021         | 62  | 0   | 96.93  | 100.00 |

| 107    | 2131         | 1   | 3   | 99.95  | 99.86  |

| 108    | 1757         | 114 | 100 | 93.51  | 94.26  |

| 109    | 2524         | 5   | 0   | 99.80  | 100.00 |

| 111    | 2118         | 4   | 0   | 99.81  | 100.00 |

| 112    | 2531         | 1   | 1   | 99.96  | 99.96  |

| 113    | 1789         | 0   | 11  | 100.00 | 99.39  |

| 114    | 1872         | 7   | 0   | 99.63  | 100.00 |

| 115    | 1946         | 0   | 0   | 100.00 | 100.00 |

| 116    | 2404         | 19  | 1   | 99.21  | 99.96  |

| 117    | 1530         | 0   | 0   | 100.00 | 100.00 |

| 118    | 2271         | 2   | 6   | 99.91  | 99.74  |

| 119    | 1981         | 0   | 52  | 100.00 | 97.44  |

| 121    | 1856         | 2   | 0   | 99.89  | 100.00 |

| 122    | 2468         | 1   | 1   | 99.96  | 99.96  |

| 123    | 1513         | 0   | 1   | 100.00 | 99.93  |

| 124    | 1613         | 1   | 1   | 99.94  | 99.94  |

| 200    | 2593         | 5   | 4   | 99.81  | 99.85  |

| 201    | 1959         | 77  | 0   | 96.07  | 100.00 |

| 202    | 2128         | 21  | 0   | 99.01  | 100.00 |

| 203    | 2973         | 72  | 17  | 97.58  | 99.42  |

| 205    | 2648         | 12  | 0   | 99.55  | 100.00 |

| 207*   | 1850         | 17  | 5   | 99.08  | 99.73  |

| 208    | 2946         | 37  | 9   | 98.74  | 99.69  |

| 209    | 2997         | 1   | 3   | 99.97  | 99.90  |

| 210    | 2642         | 135 | 4   | 94.89  | 99.84  |

| 212    | 2740         | 0   | 0   | 100.00 | 100.00 |

| 213    | 3241         | 2   | 1   | 99.94  | 99.97  |

| 214    | 2254         | 6   | 0   | 99.73  | 100.00 |

| 215    | 3353         | 5   | 2   | 99.85  | 99.94  |

| 217    | 2202         | 11  | 2   | 99.50  | 99.91  |

| 219    | 2147         | 0   | 0   | 100.00 | 100.00 |

| 220    | 2041         | 0   | 0   | 100.00 | 100.00 |

| 221    | 2420         | 14  | 0   | 99.42  | 100.00 |

| 222    | 2474         | 12  | 0   | 99.51  | 100.00 |

| 223    | 2581         | 33  | 17  | 98.72  | 99.34  |

| 228    | 2047         | 28  | 11  | 98.63  | 99.46  |

| 230    | 2248         | 0   | 1   | 100.00 | 99.96  |

| 231    | 1565         | 0   | 0   | 100.00 | 100.00 |

| 232    | 1776         | 7   | 2   | 99.61  | 99.89  |

| 233    | 3069         | 5   | 1   | 99.84  | 99.97  |

| 234    | 2745         | 0   | 0   | 100.00 | 100.00 |

| Total: | 109134       | 753 | 330 | 99.31  | 99.70  |

\* Episodes of ventricular flutter excluded from counts.

where FN meaning false negative is the number of fail detected true beats and FP meaning false positive is the number of false detected points. The detection accuracy is shown in Table III.

| Ref        | Method                     | Se (%) | Pr (%) | Area<br>(mm <sup>2</sup> ) | Power<br>(µW) | Tech.<br>(µm) | V <sub>DD</sub><br>(V) | Freq.<br>(Hz) |

|------------|----------------------------|--------|--------|----------------------------|---------------|---------------|------------------------|---------------|

| This Work# | Quadratic Spline WT        | 99.31  | 99.70  | 1.11                       | 0.83          | 0.35          | 1.8                    | 300           |

| Wang [34]^ | Pan-Tompkins               | 95.65  | 99.36  | 0.68                       | 2.21          | 0.18          | N/A                    | 500           |

| Zhang [5]& | Mathematical Morphology    | 99.81  | 99.80  | N/A                        | 2.7           | 0.35          | 3.3                    | N/A           |

| Phyu [35]  | Wavelet Multiscale-Product | 99.63  | 99.89  | 1.10                       | 176           | 0.18          | 1.8                    | 1 M           |

TABLE IV BENCHMARK OF QRS DETECTION PROCESSORS

# The power and area are also including the system controller.

^ The sensitivity / predictively results are from 5 records of MIT-BIH database

& Simulation results.

## C. Benchmark With the State-of-the-Art

A comparison with prior arts is given in Table IV. The design [34] with the Pan-Tompkins method based on band-pass filtering, nonlinear computations and threshold have limited sensitivity (Se = 95.65%) and predictivity (Pr = 99.36%), even the power consumption is impressive (2.21  $\mu$ W). The wavelet multiscale-product method [35] reports better accuracies (Se = 99.63%, Pr = 99.89%), but since RAM block is employed and the clock frequency is high, the power consumption is much higher (176  $\mu$ W). Mathematical morphology QRS detection has also been reported [5] showing high accuracies (Se = 99.80%) with low power (2.7  $\mu$ W), but the results are based on simulations. In this work, the employed Quadratic Spline WT achieves Se = 99.31%, Pr = 99.70% and 0.83  $\mu$ W of power in real-time measurements.

#### V. CONCLUSIONS

A 0.83- $\mu$ W QRS detection processor realized in a 0.35- $\mu$ m CMOS process for real-time wireless ECG monitoring has been presented. Quadratic Spline Wavelet transform provides pre-filtering, whereas the feature extraction circuits and two state machines offer modulus maxima pair recognition. Validated with all recordings in MIT-BIH arrhythmia database, the processor shows high sensitivity (99.31%) and predictivity (99.70%) in real-time tests. The system power is reduced by 6 × when compared with full-data transmission mode.

#### REFERENCES

- N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag, and A. P. Chandrakasan, "A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system," *IEEE J. Solid-State Circuits*, vol. 45, pp. 804–816, 2010.

- [2] C. Xinkai, Z. Xiaoyu, Z. Linwei, L. Xiaowen, Q. Nan, J. Hanjun, and W. Zhihua, "A wireless capsule endoscope system with low-power controlling and processing ASIC," *IEEE Trans. Biomed Circuits Syst.*, vol. 3, pp. 11–22, 2009.

- [3] J. Pan and W. J. Tompkins, "A real-time QRS detection algorithm," *IEEE Trans. Biomed. Eng.*, vol. BME-32, pp. 230–236, 1985.

- [4] R. E. Kleiger, P. K. Stein, and J. T. Bigger, "Heart rate variability: Measurement and clinical utility," *Ann. Noninv. Electrocardiol.*, vol. 10, pp. 88–101, 2005.

- [5] Z. Fei and L. Yong, "QRS detection based on multiscale mathematical morphology for wearable ECG devices in body area networks," *IEEE Trans. Biomed. Circuits Syst.*, vol. 3, pp. 220–228, 2009.

- [6] M. Ashouei, J. Hulzink, M. Konijnenburg, Z. Jun, F. Duarte, A. Breeschoten, J. Huisken, J. Stuyt, H. de Groot, F. Barat, J. David, and J. Van Ginderdeuren, "A voltage-scalable biomedical signal processor running ECG using 13 pJ/cycle at 1 MHz and 0.4 V," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, 2011, pp. 332–334.

- [7] ARM Cortex-M0 Specifications, 2011 [Online]. Available: http://www.arm.com/products/processors/cortex-m/cortex-m0.php

- [8] MSP430<sup>™</sup> The World's Lowest Power MCU, Texas Instruments Inc. [Online]. Available: http://focus.ti.com/mcu/docs/mcuorphan.tsp?contentId=61835&DCMP=MSP430&HQS=Other+OT+ulp

- [9] MSP430F20X1, MSP430F20X2, MSP430F20X3 Mixed Signal Microcontroller (Rev. H), Texas Instruments Inc. [Online]. Available: http://www.ti.com/product/msp430f2001

- [10] B. U. Kohler, C. Hennig, and R. Orglmeister, "The principles of software QRS detection," *IEEE Eng. Med. Biol. Mag.*, vol. 21, pp. 42–57, 2002.

- [11] F. A. Gari, D. Clifford, and P. E. McSharry, "ECG statistics, noise, artifacts, and missing data," in Advanced Methods and Tools for ECG Data Analysis. Norwood, MA: Artech House, 2006.

- [12] N. Thakor, J. Webster, and W. Tompkins, "Optimal QRS detector," *Med. Biol. Eng. Comput.*, vol. 21, pp. 343–350, 1983.

- [13] S. Mallat, "Translation-invariant dyadic wavelet transform," in A Wavelet Tour of Signal Processing. New York: Academic, 2009, pp. 170–178.

- [14] S. A. P. Haddad, R. Houben, and W. A. Serdijn, "Analog wavelet transform employing dynamic translinear circuits for cardiac signal characterization," in *Proc. Int. Symp. Circuits and Systems*, 2003, vol. 1, pp. I-121–I-124.

- [15] R. Sarpeshkar, "The optimum point for digitization in a mixed-signal system," in *Ultra Low Power Bioelectronics*. Cambridge, U.K.: Cambridge Univ. Press, 2010, pp. 10–14.

- [16] J. Y. S. Kwong, "Low-voltage embedded biomedical processor design," Ph.D. dissertation, Massachusetts Inst. Technol., Cambridge, MA, 2010.

- [17] L. Cuiwei, Z. Chongxun, and T. Changfeng, "Detection of ECG characteristic points using wavelet transforms," *IEEE Trans. Biomed. Eng.*, vol. 42, pp. 21–28, 1995.

- [18] P. S. Hamilton and W. J. Tompkins, "Quantitative investigation of QRS detection rules using the MIT/BIH arrhythmia database," *IEEE Trans. Biomed. Eng.*, vol. BME-33, pp. 1157–1165, 1986.

- [19] W. Zong, G. B. Moody, and D. Jiang, "A robust open-source algorithm to detect onset and duration of QRS complexes," *Comput. Cardiol.*, pp. 737–740, 2003.

- [20] V. X. Afonso, W. J. Tompkins, T. Q. Nguyen, and L. Shen, "ECG beat detection using filter banks," *IEEE Trans. Biomed. Eng.*, vol. 46, pp. 192–202, 1999.

- [21] R. Poli, S. Cagnoni, and G. Valli, "Genetic design of optimum linear and nonlinear QRS detectors," *IEEE Trans. Biomed. Eng.*, vol. 42, pp. 1137–1141, 1995.

- [22] P. E. Trahanias, "An approach to QRS complex detection using mathematical morphology," *IEEE Trans. Biomed. Eng.*, vol. 40, pp. 201–205, 1993.

- [23] P. Chaovalit, A. Gangopadhyay, G. Karabatis, and Z. Chen, "Discrete wavelet transform-based time series analysis and mining," ACM Comput. Surv., vol. 43, pp. 1–37, 2011.

- [24] S. Mallat, "Wavelet transforms," in A Wavelet Tour of Signal Processing. New York: Academic, 2009, pp. 102–115.

- [25] S. Mallat, "Algorithme à trous," in A Wavelet Tour of Signal Processing. New York: Academic, 2009, pp. 175–178.

- [26] J. P. Martinez, R. Almeida, S. Olmos, A. P. Rocha, and P. Laguna, "A wavelet-based ECG delineator: Evaluation on standard databases," *IEEE Trans. Biomed. Eng.*, vol. 51, pp. 570–581, 2004.

- [27] S. Mallat and S. Zhong, "Characterization of signals from multiscale edges," *IEEE Trans. Pattern Anal. Mach. Intell.*, vol. 14, pp. 710–732, 1992.

- [28] C. T. Ma, P. I. Mak, M. I. Vai, P. U. Mak, S. H. Pun, W. Feng, and R. P. Martins, "Frequency-bandwidth-tunable powerline notch filter for biopotential acquisition systems," *Electron. Lett.*, vol. 45, pp. 197–199, 2009.

- [29] X. Qian, Y. Xu, and X. Li, "A CMOS continuous-time low-pass notch filter for EEG systems," *Analog Integr. Circuits Signal Process.*, vol. 44, pp. 231–238, 2005.

- [30] MIT-BIH Arrhythmia Database [Online]. Available: http://www.physionet.org/physiobank/database/mitdb

- [31] AHA Database Sample Excluded Record [Online]. Available: http:// www.physionet.org/physiobank/database/ahadb

- [32] Low-Cost Low-Power 2.4 GHz RF Transceiver (Rev. C) [Online]. Available: http://focus.ti.com/docs/prod/folders/print/cc2500.html

- [33] R. F. Yazicioglu, P. Merken, R. Puers, and C. Van Hoof, "A 60 μW 60 nV/√Hz readout front-end for portable biopotential acquisition systems," *IEEE J. Solid-State Circuits*, vol. 42, pp. 1100–1110, 2007.

- [34] W. Hui-Min, L. You-Liang, M. C. Hou, L. Shih-Hsiang, B. S. Yen, H. Yu-Chieh, C. Lei-Chun, H. Shao-You, H. Sheng-Chieh, and J. Ming-Yie, "A ±6 ms-accuracy, 0.68 mm<sup>2</sup> and 2.21 μW QRS detection ASIC," in *Proc. IEEE Int. Symp. Circuits and Systems*, 2010, pp. 1372–1375.

- [35] P. M. Wai, Z. Yuanjin, Z. Bin, X. Liu, and W. Y. Sheng, "A real-time ECG QRS detection ASIC based on wavelet multiscale analysis," in *Proc. IEEE Asian Solid-State Circuits Conf.*, 2009, pp. 293–296.

Chio-In leong received the B.Sc. degree in communication engineering and minored in computer science and technology from Sun Yat-Sen University, Guangzhou, China, in 2003, and the M.Sc. degree from the Department of Electrical and Electronics Engineering (now Electrical and Computer Engineering), University of Macau, Macao, China, in 2008.

He is currently pursuing the Ph.D. degree in the Department of Electrical and Computer Engineering, University of Macau. He has served as a Teacher in-

structing mathematics and physics, and led a robot team in middle school. He has been a Graduate Assistant tutoring microprocessors, digital controllers, digital signal processing, communication system, and data network Bachelor-level courses, and a Research Assistant in Biomedical Engineering Lab, University of Macau. His current research interests include biomedical signal processing, compressed sensing, power-efficient VLSI circuits and systems, and machine intelligence.

Pui-In Mak (S'00–M'08–SM'11) received the B.S.E.E.E. and Ph.D.E.E.E. degrees from the University of Macau (UM), Macao, China, in 2003 and 2006, respectively. He has been with the UM State Key Laboratory

of Analog and Mixed-Signal VLSI as a Research Assistant (2003–2006), Invited Research Fellow (2006–2008) and Coordinator of the Wireless and Biomedical Research Lines (2008–present). He is currently an Associate Professor at UM (2008–present). He had short-term work with

Chipidea Microelectronics (2003), and was a Visiting Scholar at the University of Cambridge, U.K. (2009), INESC-ID, Portugal (2009) and University of Pavia, Italy (2010). His current research interests are in analog/RF circuits and systems for wireless, biomedical and physical chemistry, and engineering education.

Dr. Mak has authored two books, Analog-Baseband Architectures and Circuits for Multistandard and Low-Voltage Wireless Transceivers (Springer, 2007), and High-/Mixed-Voltage Analog and RF Circuit Techniques for Nanoscale CMOS (Springer, 2012), and more than 90 papers in refereed journals and conferences. He holds three U.S. patents and has several under application. He is an Associate Editor of IEEE TRANSACTION ON CIRCUITS AND SYSTEMS I-REGULAR PAPERS (2010–2011), IEEE TRANSACTIONS ON CIRCUITS

AND SYSTEMS II–EXPRESS BRIEFS (2010–2011), and IEEE Circuits and Systems Society (CASS) Newsletter (2010present). He is a member of the CASS Board of Governors (2209–2011). CASS Publication Activities Committee (2009–2011) and CASS Technical Committees of CASCOM (2008–present) and CASEO (2009–present). He has served on the Technical/Organization Committees of numerous conferences including AVLSIWS'04, APCCAS'08, PrimeAsia'09–11, ISCAS'10, VLSI-SoC'11, SENSORS'11, RFIT'11, and APCCAS'12. He co-organized the GOLD Sessions in ISCAS (2009–2011).

Dr. Mak was the corecipient of eight paper awards including one in the DAC/ ISSCC Student Paper Contest 2005. He was the recipient of a government decoration, Honorary Title of Value 2005 for scientific merits; the University of Cambridge Visiting Fellowship 2009; the IEEE MGA GOLD Achievement Award 2009; the CASS Chapter of the Year Award 2009; the UM Research Award 2010; the IEEE CASS Outstanding Young Author Award 2010, and the UM Academic Staff Award 2011.

**Chi-Pang Lam** received the B.S. and M.S. degrees from the Department of Electrical Engineering, National Taiwan University (NTU), Taiwan, in 2007 and 2009, respectively. He is currently pursuing the Ph.D. degree at the University of California, Berkeley.

He was a Senior Engineer at MStar Semiconductor, Taiwan, and a Research Assistant in Advanced Control Laboratory, NTU. Before he pursued the Ph.D. degree, he served as a Research Assistant in the Biomedical Engineering Laboratory, University of Macau, Macao, China. His research learning control theory and robotics

interests include machine learning, control theory, and robotics.

**Cheng Dong** is a Master student in the Department of Electrical and Computer Engineering, University of Macau, Macao, China. His research interests are in the design and implementation of algorithms in the field of heart beat detection, ECG delineation, and heart rate variability analysis.

**Mang-I Vai** (SM'06) received the Ph.D. degree in electrical and electronics engineering from the University of Macau, Macao, China, in 2002.

Since 1984, he has been involved in research in the areas of digital signal processing and embedded systems. He is currently an Associate Professor and the Head of the Department of Electrical and Electronics Engineering, Faculty of Science and Technology, University of Macau.

**Peng-Un Mak** (S'88–M'97–SM'11) received the B.Sc. degree from National Taiwan University, Taipei, Taiwan, and the M.Sc. and Ph.D. degrees from Michigan State University, East Lansing, all in electrical engineering.

Since 1997, he has been an Assistant Professor in the Department of Electrical and Electronics Engineering, University of Macau, Macao, China. He has authored/coauthored more than 100 peer-reviewed technical publications (journals, book chapters, conference proceedings etc.). His current research

interests include bioelectromagnetism, intrabody communication, and bioelectric signals acquisition.

**Sio-Hang Pun** received the Master degree in computer and electrical program from the University of Porto, Porto, Portugal, in 1999, and the Ph.D. degree in electrical and electronics engineering from the University of Macau, Macao, China, in 2011.

Since 2000, he has performed research in the area of biomedical engineering. His research interests are bioelectronic circuits, intra-body communications, and bioelectromagnetism. He is currently an Assistant Professor of the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau.

Feng Wan received the Ph.D. degree from the Hong Kong University of Science and Technology, Hong Kong, China.

He is currently an Assistant Professor in the Department of Electrical and Computer Engineering, Faculty of Science and Technology, University of Macau, Macao, China. His research interests include biomedical signal processing, brain-computer interfaces, computational intelligence, and intelligent control.

**Rui P. Martins** (M'88–SM'99–F'08), was born on April 30, 1957. He received the Bachelor (5 years), the Masters, and the Ph.D. degrees as well as the Habilitation for Full Professor in electrical engineering and computers from the Department of Electrical and Computer Engineering, Instituto Superior Técnico (IST), TU of Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

He has been with the Department of Electrical and Computer Engineering/IST, TU of Lisbon, since October 1980. Since 1992, he has been on leave from IST, TU of Lisbon, and is also with the Department of Electrical and Computer Engineering, Faculty of Science and Technology (FST), University of Macau (UM), Macao, China, where he is a Full Professor since 1998. In FST he was the Dean of the Faculty from 1994 to 1997 and he has been Vice-Rector of the University of Macau since 1997. From September 2008, after the reform of the UM Charter, he was nominated after open international recruitment as Vice-Rector (Research) until August 31, 2013. Within the scope of his teaching and research activities he has taught 20 bachelor and master courses and has supervised 24 theses: 11 Ph.D. and 13 Masters. He has published: 16 books, coauthoring five and coediting 11, plus five book chapters; 204 refereed papers in scientific journals (38) and in conference proceedings (166); as well as 70 other academic works, in a total of 295 publications. He has coauthored three U.S. Patents (one issued in 2009 and two in 2011) and has also submitted four others (one patent pending and three under application). He has created the Analog and Mixed-Signal VLSI Research Laboratory of UM (http://www.fst.umac.mo/en/lab/ans vlsi/website/index.html), recently elevated to State Key Lab of China (the first in engineering in Macao), being its Founding Director. He is the financial manager, recognized by EU, of a Jean Monnet Chair in EU Law - Facing the Constitution and Governance Challenges in the Era of Globalization, unique in the universities from HK and Macao, for the period 2007 to 2012.

Dr. Martins was the Founding Chairman of the IEEE Macau Section from 2003 to 2005, and of the IEEE Macau Joint Chapter on Circuits and Systems (CAS)/Communications (COM) from 2005 to 2008 [2009 World Chapter of the Year of the IEEE Circuits and Systems Society (CASS)]. He was the General Chair of the 2008 IEEE Asia-Pacific Conference and Circuits and Systems (APCCAS'08) and was elected Vice President for Region 10 (Asia, Australia, the Pacific) of the IEEE Circuits and Systems Society (CASS), for the period of 2009 to 2012. He is an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II–EXPRESS BRIEFS, for the period of 2010 to 2011. He was the recipient of two government decorations: the Medal of Professional Merit from Macao Government (Portuguese Administration) in 1999, and the Honorary Title of Value from Macao SAR Government (Chinese Administration) in 2001. In July 2010 he was elected, unanimously, as Corresponding Member of the Portuguese Academy of Sciences.