# A 4-b 7-μW Phase Domain ADC With Time Domain Reference Generation for Low-Power FSK/PSK Demodulation

Xuewei Lei, Chi-Hang Chan<sup>®</sup>, *Member, IEEE*, Yan Zhu<sup>®</sup>, *Senior Member, IEEE*, and Rui Paulo Martins<sup>®</sup>, *Fellow, IEEE*

Abstract—This paper presents a 4-b phase-domain analog-todigital converter (ADC) that utilizes the time-domain reference generation scheme for low-power operation. Rather than prior arts that rely on power-hungry resistive/current combiners or the IQ-assisted binary-search algorithm with large power T&H circuits for the reference generation, this design benefits from the fully dynamic power characteristic of the time-domain operation, thus leading to an energy-efficient phase ADC design. By introducing several on-chip calibration techniques, the design achieves good robustness with the proposed time-domain operation. The prototype is fabricated in the standard 65-nm CMOS technology, achieving an ENOB of 3.42 bits at 1 MS/s with near Nyquist input, while dissipating 7  $\mu$ W from a 1-V supply. It leads to a 1.36-pJ/conversion-step Walden Figure of Merit at Nyquist input (FoM@Nyquist).

*Index Terms*—Bluetooth low energy (BLE), frequency-shift keying (FSK), low power, phase ADC.

## I. INTRODUCTION

**W**EARABLE and portable devices are going to take part and become the major participant in Internet of Things (IoT) systems. In order to extend the battery life and meet the IoT standard, the ultra-low power consumption becomes a key feature. Bluetooth Low Energy (BLE) is a promising solution for the information linking in IoT applications as it consumes a relatively low power compared with other technologies [1]–[3]. The adopted modulation scheme in the BLE system is Gaussian Frequency-Shift Keying (GFSK), which is widely used in low-cost and short-range applications due to its spectral efficiency and constant envelope property [4], [5].

Manuscript received March 15, 2019; revised May 20, 2019; accepted June 4, 2019. Date of publication July 12, 2019; date of current version August 28, 2019. This work was supported in part by the Macao Science and Technology Development Fund under Grant 006/2018/A2 and in part by the Research Grant from the University of Macau under Grant MYRG2018-00113-AMSV. This paper was recommended by Associate Editor Y. LU. (*Corresponding author: Yan Zhu.*)

X. Lei, C.-H. Chan, and Y. Zhu are with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macau 999078, China (e-mail: yanzhu@umac.mo).

R. P. Martins is with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macau 999078, China, and also with the Department of Electrical and Computer Engineering, Faculty of Science and Technology, University of Macau, Macau 999078, China, on leave from the Instituto Superior Técnico, Universidade de Lisboa, 1000-029 Lisbon, Portugal.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2019.2921791

In Frequency-Shift Keying (FSK) demodulation, the phase signal is extracted from the baseband in-phase signal I and the quadrature signal Q. Conventionally, I and Q signals are quantized by two amplitude analog-to-digital converters (IQ ADCs), and the subsequent demodulation is processed in the digital domain [6]–[9]. According to [10], the IQ ADC needs extra 0.49 bit to accommodate a non-constant vector magnitude of the phase input; otherwise, an automatic gain control (AGC) is needed to trim the magnitude of the vector. An alternative to get around the above issue is to quantize the signal in phase domain directly. A phase ADC converts the phase information into digital codes regardless of the input amplitude that obtains an inherent immunity to the magnitude variation, therefore significantly relaxed the requirement of AGC. Another benefit is that the additional digital overhead for demodulation can be avoided as the quantization is based on the signal's phase, eventually saving the area and power consumption.

With the standard modulation index h = 0.5 of BLE, the phase of symbol "1" is 90°, and the phase of symbol "0" is  $-90^{\circ}$  [5]. Considered the conventional BLE symbol rate of 1 MHz with the baseband frequency of 250 kHz, a 2-bit phase ADC with phase LSB = 90° (250 k/1 M × 360°) is sufficient to detect the symbol. In practice, the signals at the transmitter and the receiver side have a frequency deviation of  $\pm 150$  kHz, resulting in a frequency variation from 100 to 400 kHz in the receiver [4]. Meanwhile, the phase difference of each symbol in the system varies from 36° to 144°. Therefore, to tolerate this frequency variation, a 4-bit phase domain ADC with a quantization step of 22.5° operating at 1 MS/s is required.

To achieve the above specifications, several phase ADC architectures were investigated in the literature. In [4] and [9], two full-flash architectures are reported, where they both detect zero-crossings in the rotated versions of the initial phase to determine the input phase condition. However, such architectures demand linear resistive/current combiners that consume static current to generate phase shifted sinusoids for zero-crossing detections, thus consuming a large power dissipation [4], [9]. Another phase ADC explores a binary-search IQ-assisted algorithm [11], [12] that omits the linear combiner and reduces the number of comparisons from  $2^{N-1}$  in Flash to N + 1 for an N-bit phase ADC [11]. Nevertheless, both

1549-8328 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

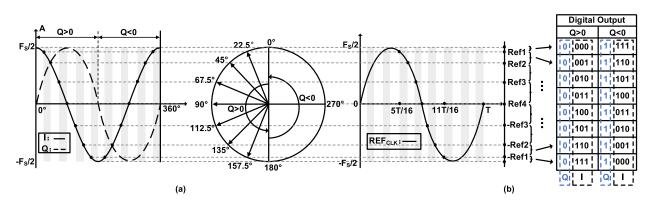

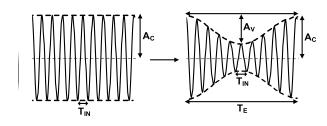

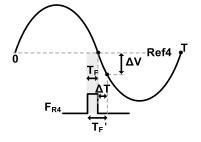

Fig. 1. (a) Phase intervals definition, (b) time to voltage definition and the corresponding digital outputs.

voltages of the I and the Q signals are necessarily tracked and then held by an active track-and-hold (T&H) circuit as well as a charge-redistribution DAC [12]. Since the I and the Q signals may behave as reference voltages of the DAC during the conversion [12], a power-hungry T&H circuit [11], [12] is essential in order to achieve a sufficient conversion accuracy.

In this paper, a phase ADC based on the time domain operation is presented. Unlike previous works, its references are realized based on the time manner, thus avoiding the power-hungry linear combiners or active T&H circuits. Benefiting from the time domain operation, the ADC only consumes dynamic power; therefore, it obtains a better energy efficiency and becomes more scaling friendly. The prototype is fabricated in the 65-nm CMOS technology. It also achieves an Effective Number of Bits (ENOB) of 3.42 bits at near Nyquist input and consumes 7  $\mu$ W power from a 1 V supply when running at 1 MS/s, resulting in an FoM of 1.36 pJ/conversion-step.

The rest of the paper is organized as follows. In Section II, the proposed principles, the ADC architecture and the envelope variations are described, followed by a detailed description of the circuits in Section III. Measurement results are presented in Section IV. Finally, Section V gives the conclusion.

#### II. ADC ARCHITECTURE AND ENVELOPE VARIATION

## A. ADC Architecture and Operation

In Phase-Shift-Keying (PSK) and FSK, the phase information  $\varphi$  is represented by two quadrature signals *I* and *Q*, which equal to  $\cos\varphi$  and  $\sin\varphi$ , respectively [4]. To convert the phase information of this pair of quadrature signals into digital with a 4-bit phase quantizer, the full-scale phase (0°-360°) is equally divided into 16 intervals, as illustrated in Fig. 1(a) where Q > 0/Q < 0 corresponds to the signal range of 0° <  $\varphi < 180^{\circ}/180^{\circ} < \varphi < 360^{\circ}$ . The *I* signal is splitted into 8 voltage regions. If the values of *I* and *Q* of an unknown phase  $\varphi$  are given, by mapping the value of *I* to those 8 regions and identifying the polarity of *Q*,  $\varphi$  can be easily resolved.

Conventionally, to obtain the voltage references for such 8 regions, a combiner which is similar to the current steering is required, thus leading to an inevitable quiescent current. Instead, we proposed a time-domain reference generation technique that consumes only dynamic power. In the receiver end, a reference clock signal ( $\text{REF}_{\text{CLK}}$ ) is necessary to identify

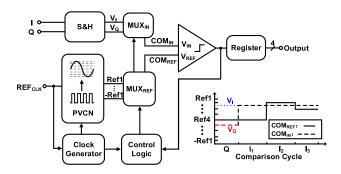

Fig. 2. ADC architecture and conversion diagram.

the baseband signals. With a period T and a normalized amplitude with I and Q signals, REF<sub>CLK</sub> is divided into 16 identical time intervals (T/16). The corresponding 7 references (with 8 regions) can be obtained at the crossing points between the 16 interval instants and the REF<sub>CLK</sub> (Fig. 1(b)), where Ref1, Ref2, ..., -Ref1 are corresponding to 5T/16, 6T/16, ..., 11T/16 time interval crossing points, respectively. Such 7 references can be easily sampled and stored in a capacitive network (Fig. 2), consuming a very low dynamic power. With these 7 intervals and a Phase-to-Voltage Capacitive Network (PVCN), the complex and power hungry resistive/current combiners [4], [9] or monotonic nonlinear unary DAC [12] in prior phase ADC designs can be avoided.

Fig. 2 shows the proposed ADC architecture. It consists of a passive S&H circuit for the input sampling, a PVCN for the reference generation, a comparator, a clock generator, a control logic, a register and two MUXes (MUX<sub>IN</sub> and MUX<sub>REF</sub>). The PVCN, which is designed according to the time domain concept introduced in the previous section, generates all the 7 references by co-working with the clock generator. The MUX<sub>IN</sub> selects *I* or *Q* signal sampled by the S&H circuit for comparison while MUX<sub>REF</sub> selects one of the reference levels to compare. The operation is similar to a Successive-Approximation Register (SAR) ADC that provides a binary-searched feedback according to the decision of the comparator in the phase domain. REF<sub>CLK</sub> is the sinusoid signal that is used to generate the 7 reference levels and simultaneously severs as the master clock for our ADC.

The I and Q signals are first sampled by the S&H circuit in the sampling phase that is followed by the reference generation

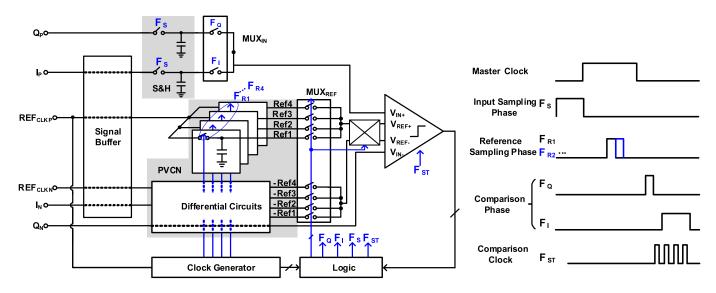

Fig. 3. ADC implementation and timing diagram.

phase. In the comparison phase, the MUX<sub>IN</sub> selects the Q signal while MUX<sub>REF</sub> selects Ref4 for the MSB determination that signs the polarity of Q. Afterwards, the V<sub>I</sub> signal is selected and compared with ±Ref1-3 in the successive approximation manner. As the example shown in Fig. 2, the comparison starts from Ref4, and the decision of the comparator controls MUX<sub>REF</sub> to choose the next reference level (Ref2 in this case) for MSB/2. The procedure repeats 3 times to quantize a 4-bit phase resolution.

## **B.** ADC Implementation

The specific implementation of the phase ADC is depicted in Fig. 3. For simplicity, only the positive side of the circuit is shown, as the negative counterpart is identical. A signal buffer circuit is added to serves as a voltage buffer for both I and REF<sub>CLK</sub> signals. However, if voltage buffers are inherently available, such signal buffer can be omitted.

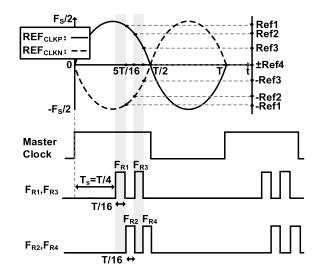

To generate the reference levels, the PVCN, which consists of a simple switch-capacitor network controlled by  $F_{R1\sim4}$ (in Fig. 4), samples 4 times of the REF<sub>CLK</sub> in 4 equivalent time intervals.  $F_{R1\sim4}$  are four non-overlapped clocks having a fixed delay of 1/4T, 5/16T, 3/8T and 7/16T with the master clock respectively and pulse widths of T/16. When the reference generation phase ends, the voltage references are stored in the PVCN. Once the input and references are ready, the quantization is triggered by  $F_{ST}$  (the clock of the dynamic comparator).

In the last two comparison cycles of V<sub>I</sub>, where V<sub>I</sub> needs to compare with negative references (-Ref1 to -Ref3), the positive references and the negative references are swapped from the comparator's V<sub>REF+</sub> to V<sub>REF-</sub> side. For example, if the decision of the first comparison of *I* which is comparing with Ref4 is "0", implying that it is smaller than Ref4, V<sub>I</sub> will compare to -Ref2 in the next comparison cycle. As shown in Fig. 3, sampled reference -Ref2 is at V<sub>REF-</sub> side, but -Ref2 is required to connect to V<sub>REF+</sub> to make the comparison. Therefore, -Ref2 is swapped from

Fig. 4. Reference sampling timing diagram.

$V_{REF-}$  to  $V_{REF+}$ , and meanwhile Ref2 is swapped from  $V_{REF+}$  to  $V_{REF-}$ . The cases of -Ref1 and -Ref3 are similar.

### C. Envelope Variation

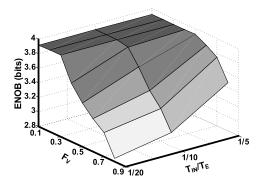

As described in the introduction section, the phase ADC has a certain ability to reject the magnitude variation of the input signals. To show the influence of the magnitude variations on our phase ADC, a simulation in which the envelope of the signals (I, Q and REF<sub>CLK</sub>) are varying with time in a sinusoid fashion (Fig. 5) is conducted. The varying period of the envelope is T<sub>E</sub>, and the period of the input signals (I and Q) is T<sub>IN</sub>. A<sub>C</sub> is the constant envelope amplitude, and A<sub>V</sub> is the largest variation of the envelope from the constant amount. To further quantify the variation, a variation factor F<sub>V</sub> which equals to the value of A<sub>V</sub>/A<sub>C</sub> is defined. Fig. 6 shows the ENOB variation versus the F<sub>V</sub> variation under different values of T<sub>IN</sub>/T<sub>E</sub>.

In receiver systems, AGCs are always required since the envelope variations can be significant. The ADC used in

Fig. 5. Example of envelope variation diagram.

Fig. 6. ENOB versus F<sub>V</sub> and T<sub>IN</sub>/T<sub>E</sub>.

Fig. 7. Overall clock generator block diagram.

receiver systems for variable gain control should provide amplitude information of the received signals; thus, an amplitude ADC is necessary to detect the envelope information. In other words, an amplitude ADC and a phase ADC are both required . However, the resolution of the amplitude ADC and the performance of the gain control can be much more relaxed because of the robustness of phase ADC to the envelope variation. As an example, the PGA in [4] only implements a coarse gain step of 6 dB because of the large tolerance of envelope variation of the phase ADC.

#### **III. CIRCUIT IMPLEMENTATION**

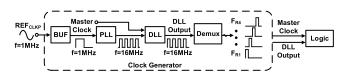

## A. Clock Generator

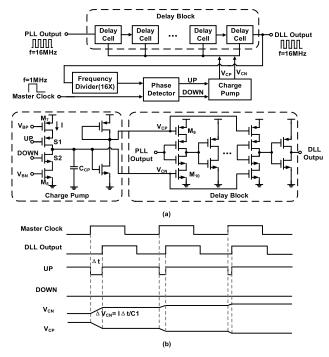

The clock generator illustrated in Fig. 7 consists of a buffer, a Phase-Locked Loop (PLL) block, a Delay-Lock Loop (DLL) block and a De-multiplexer (Demux). The REF<sub>CLKP</sub> first passes through the buffer to generate the master 1 MHz clock. Feeding the master clock to the PLL, a 16 MHz clock is obtained, and the 16 MHz clock passes through the DLL block to align with the master clock. The Demux separates the 16 MHz DLL output to four 1 MHz reference sampling clocks as  $F_{R1-4}$ . The master clock and the DLL output are also fed to the logic circuit for further control signals generation.

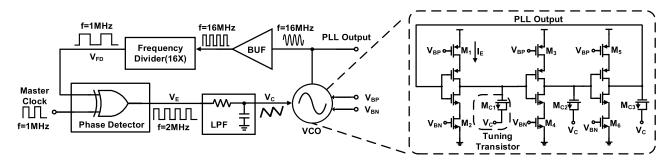

1) PLL: The PLL block is a feedback system that includes a voltage-controlled oscillator (VCO), a frequency divider, a phase detector and a low pass filter within its loop. Its purpose is to ensure that the VCO generates a 16 MHz output under a 1 MHz input reference clock. Fig. 8 shows the PLL block diagram. The output of the VCO is fed to the phase detector after the buffer and the frequency divider. The frequency divider divides the frequency of VCO by 16, and the phase detector detects the frequency difference between the master clock and the output signal of the frequency divider, where their frequency difference is translated into the pulse width of  $V_E$ .  $V_E$  is then transformed to  $V_C$  by the low pass filter (LPF) to generate the control voltage for adjusting the output frequency of the VCO.

When the feedback loop stabilizes, the PLL output frequency remains oscillating around 16 MHz due to the variation of V<sub>C</sub>. This variation of the PLL output frequency potentially causes sampling mismatches of 7 reference levels, ultimately leading to conversion errors. Based on the simulation result, when the voltage variation of the reference voltages exceeds  $\pm 37$  mV (most critical case), the signal-to-noise-and-distortion ratio (SNDR) of the phase ADC drops 3 dB. As shown in Fig. 9, this voltage variation  $\Delta V$  can be referred to the pulse width variation  $\Delta T$  and further to the PLL's period variation  $T_F'$  which can be calculated as:

$$T_{F}^{'} = \frac{\arcsin[\sin(\frac{8\pi}{16}) - \Delta V] - \frac{8\pi}{16}}{2\pi} \times T + T_{F}, \quad (1)$$

where T is the period of REF<sub>CLK</sub>. Based on (1) with T = 1 $\mu$ s,  $\Delta V = \pm 37$  mV and T<sub>F</sub> = 62.5 ns, the T<sub>F</sub>' is  $\pm 6$  ns, and the equivalent PLL frequency drift should be within 14.6 MHz - 17.7 MHz in order to have less than 3 dB SNDR degradation. The frequency variation is further translated into the requirement of the K<sub>VCO</sub> which defines the frequency variation when V<sub>C</sub> varies by 1 V. In our design, even when sizing M<sub>C1-3</sub> to minimum width and length, a K<sub>VCO</sub> of 0.5 MHz/V is achieved which can tolerate a 0.5 V variation of V<sub>C</sub> in one cycle. The VCO is implemented by three (minimum number of inverters for VCOs to oscillate) inverter-based delay stages and all the transistors are in minimum sizes.

2) *DLL*: The DLL block is implemented to ensure that the 16 MHz reference sampling clock aligns with the master one so that accurate references can be obtained. The block diagram is illustrated in Fig. 10(a) together with a charge pump and a delay block circuit schematic. It contains a delay block, a frequency divider, a phase detector and a charge pump. After passing the delay blocks, the DLL output is divided by 16. Then its phase is compared with the master 1 MHz clock in the phase detector, where their phase difference is transferred to the pulse width of the output signals UP and DOWN. The charge pump generates  $V_{CP}$  and  $V_{CN}$  from UP and DOWN to control the delay of the delay cells. The phase of the DLL output can be adjusted to synchronize with the master clock.

The phase synchronization accuracy is determined by the delay time variation of the DLL circuit  $\Delta t$  as illustrated in Fig. 10(b). Based on the analysis in the previous PLL section, such delay time variation should be within  $\pm 6$  ns. To ensure this  $\pm 6$  ns variation requirement of  $\Delta t$ after the DLL stabilizes, the V<sub>CN</sub> has to be designed with 150 mV variation to cover 0-62.5 ns delay variation while at the same time preventing M<sub>9</sub> and M<sub>10</sub> from entering the

Fig. 8. PLL block diagram.

Fig. 9. Frequency variation diagram.

Fig. 10. DLL (a) block diagram and (b) timing diagram.

sub-threshold region. Thus, the equivalent  $\Delta V_{CN}$  for  $\pm 6$  ns variation of  $\Delta t$  should be within 28.8 mV as 150 mV/62.5 ns =  $\Delta V_{CN}/12$  ns. Since  $\Delta V_{CN} = I\Delta t/C_{CP}$ , the value of  $I/C_{CP}$  should be smaller than  $2.4 \times 10^6$ . If a 30 fF value is chosen for  $C_{CP}$ , the current I requires a value smaller than 72 nA. By implementing  $M_7$  and  $M_8$  as hvt MOS transistors and the sizes to minimum can meet the requirement of the DLL.

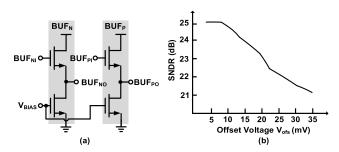

## B. Signal Buffer With Offset Cancellation

Before the sampling, the input I and the REF<sub>CLK</sub> are passed through a signal buffer which indeed includes two buffers (BUF<sub>P</sub> and BUF<sub>N</sub>) and an offset cancellation circuit (four capacitors and some switches). The two identical

Fig. 11. (a) Buffer diagram and (b) relationship between offset voltage and SNDR.

buffers (shown in Fig. 11(a)) built with simple source-follower topology are implemented for buffering the signal (I) and the reference (REF<sub>CLK</sub>), as well as avoiding the switches' kickbacks to the front analog circuit. BUF<sub>NI</sub> and BUF<sub>PI</sub> are the input terminals; BUF<sub>NO</sub> and BUF<sub>PO</sub> are the output terminals. V<sub>BIAS</sub> is the biasing voltage for the buffers.

Due to the device mismatches, the output common mode voltages of  $BUF_P$  and  $BUF_N$  are different, which introduces references mismatches and eventually degrading the conversion accuracy. To demonstrate the design sensitivity to the offset, Fig. 11(b) plots the offset voltage  $V_{ofs}$  versus the SNDR. The buffers indicate one sigma offset mismatches of 40 mV from Monte Carlo simulations, which leads to more than 4 dB SNDR drop. Therefore, the offset cancellation technique is proposed to fix the offset mismatches from the input buffers.

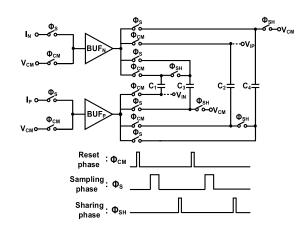

Fig. 12 shows the detailed circuit implementation and its timing diagram. The offset cancellation is processed in three phases. Firstly, the offsets from the buffers are sampled and stored at the output loading capacitor ( $C_1 \& C_2$ ) by resetting the input to  $V_{CM}$  ( $\Phi_{CM} = 1$ ). Then the input sampling phase starts ( $\Phi_S = 1$ ), where the differential inputs *I* are double sampled onto  $C_3$  and  $C_4$ , respectively. To cancel the offset in  $C_3$  and  $C_4$  ( $\Phi_{SH} = 1$ ), they are connected in series with  $C_1$  and  $C_2$ , respectively. The offset polarities of two series connected capacitors are opposite. Thus, they cancel out after sharing. Output voltages are  $V_{IP}$  and  $V_{IN}$ . The final signal amplitude remains the same as the input signal since the double sampling is used to amplify the signal by 2.  $C_{1-4}$  have the same capacitance of 10 fF.

#### C. Comparator

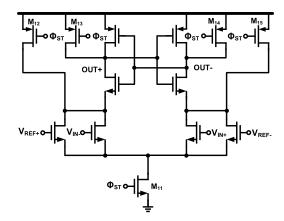

The four-input comparator circuit schematic is depicted in Fig. 13. The comparator is StrongArm architecture with NMOS input pairs. Both the reference and the input pairs

Fig. 12. Offset calibration circuit and timing diagram.

Fig. 13. Comparator circuit schematic.

Fig. 14. Die micro photograph.

share the same branch and tail switches. When  $\Phi_{ST} = 0$ , transistors  $M_{12-15}$  are on, and  $M_{11}$  is off to reset the outputs of the comparator (OUT+/-) to the supply voltage. When  $\Phi_{ST}$  changes from the ground to the supply voltage, the tail transistor  $M_{11}$  is on, and  $M_{12-15}$  are off, then a current path from the supply to the ground is conducted. The input and reference voltages are converted from the voltage to current domain through the input and reference pair transistors. Such current difference triggers the regeneration process of the back-to-back inverter and gives a decision at the output of the comparator. A latch circuit follows the comparator to ensure a fast and valid regeneration process within a given time.

TABLE I Performance Comparison

|                             | [4]                 | [11]                       | This work                   |

|-----------------------------|---------------------|----------------------------|-----------------------------|

| Technology(µm)              | 0.13                | 0.18                       | 0.065                       |

| Architecture                | Current<br>Combiner | Charge -<br>Redistribution | Time Domain<br>Quantization |

| Power Supply(V)             | 1                   | 1.2                        | 1                           |

| Resolution(bits)            | 4                   | 5                          | 4                           |

| Sampling<br>Rate(MS/s)      | 1                   | 1                          | 1                           |

| Power<br>Consumption(µW)    | 25                  | 12.9                       | 7**                         |

| ENOB@ Nyq(bits)             | 3.61*               | 3.36                       | 3.42                        |

| Chip Area(mm <sup>2</sup> ) | 0.015               | 0.059                      | 0.0035                      |

| FoM(pJ/c-s)                 | 16.6*               | 2.5                        | 1.36                        |

\*:Input frequency at 123.1kHz. ENOB at Nyquist rate is not provided. \*\*: Including signal buffer power.

Fig. 15. Power breakdown of the phase ADC.

Fig. 16. Measured spectrum (2048-point FFT) at near Nyquist input.

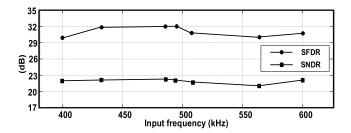

Fig. 17. SNDR and SFDR variation with input frequency.

## IV. MEASUREMENT RESULTS

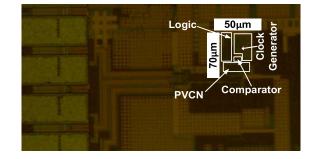

This 4-bit 1 MS/s phase ADC was fabricated in the 65-nm CMOS technology. The occupied active core area is 70  $\mu$ m × 50 $\mu$ m as shown in the microphotograph in Fig. 14.

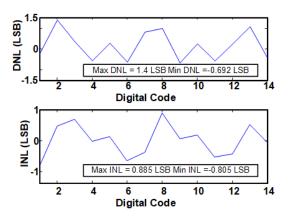

Fig. 18. Measured DNL and INL.

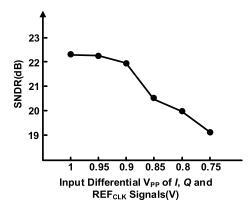

Fig. 19. Measured SNDR as a function of the differential  $V_{PP}$  voltages of the *I*, *Q* and REF<sub>CLK</sub> signals.

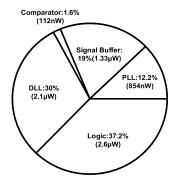

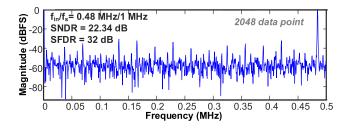

The phase ADC works under a 1 V power supply and consumes only 7  $\mu$ W power at 1 MS/s thanks to the proposed fully dynamic reference generation scheme. Fig. 15 shows the power breakdown diagram. The power consumption of the comparator, the signal buffer, the PLL circuit, the DLL circuit and the logic circuits are 112 nW, 1.33  $\mu$ W, 854 nW, 2.1  $\mu$ W and 2.6  $\mu$ W, respectively. Different from voltage domain ADCs, the phase is considered as the variable of the ADC input for the dynamic measurement of phase ADCs. Therefore, the Q input signal is set to  $A\sin[\pi \sin(2\pi ft)]$ , where A stands for the amplitude of Q, f stands for the frequency and t stands for time. Likewise, the I input signal is set to  $I = A\cos[\pi \sin(2\pi ft)]$  to match the Q counterpart. Fig. 16 shows the ADC output spectrum with input phase frequency of 0.48 MHz. The measured phase SNDR is 22.35 dB, resulting in a 3.42 bits ENOB at this near Nyquist input. The measured SNDR and the spurious-free dynamic range (SFDR) with input frequency sweeping are plotted in Fig. 17. It can be observed that SNDR and SFDR basically remained unchanged even the phase input rises to high frequency (above Nyquist). It is worth noting that, due to input transformer limitation, a low-frequency phase input cannot be provided. The measured differential nonlinearity (DNL) and integral nonlinearity (INL) values are shown in Fig. 18. Fig. 19 depicts the measured SNDR as a function of the differential peak-to-peak

voltages (V<sub>PP</sub>) of the *I*, *Q* and REF<sub>CLK</sub> signals. When the V<sub>PP</sub> voltage decreases to 0.75 V, the SNDR of the phase ADC drops about 3 dB. The FoM used in table I is defined by:

$$FoM = \frac{P}{2^{ENOB} \times f_{in}},\tag{2}$$

where P is the power consumption of the ADC, ENOB is the effective number of bits when the input is at Nyquist frequency, and  $f_{in}$  is the Nyquist input frequency. Table I shows the comparison of the proposed ADC with other state-of-theart works. The proposed ADC demonstrates the best power efficiency with a small area.

#### V. CONCLUSION

In this paper, a low power phase ADC with time-domain reference generation concept is proposed. Benefitted from the fully dynamic power dissipation, the ADC achieves an outstanding FoM and attains a compact area. With only 7  $\mu$ W power consumption at 1 MS/s, the ADC obtains an FoM at Nyquist input of 1.36 pJ/conversion-step, which is a suitable design for low power communication system based on the phase modulation scheme.

#### REFERENCES

- F. Vasconcelos, L. Figueiredo, A. Almeida, and J. C. Ferreira, "SMART sensor network: With Bluetooth low energy and CAN-BUS," in *Proc. IEEE Int. Conf. Service Oper. Logistics, Inform.*, Sep. 2017, pp. 217–223.

- [2] A. Yousefi, K. Somaratne, and F. J. Dian, "Analysis of time synchronization based on current measurement for Bluetooth Low Energy (BLE)," in *Proc. IEEE Annu. Inf. Technol., Electron. Mobile Commun. Conf. (IEMCON)*, Oct. 2017, pp. 602–607.

- [3] K. V. Ritesh, A. Manolova, and M. Nenova, "Abridgment of Bluetooth low energy (BLE) standard and its numerous susceptibilities for Internet of Things and its applications," in *Proc. IEEE Int. Conf. Microw., Antennas, Commun. Electron. Syst. (COMCAS)*, Nov. 2017, pp. 1–5.

- [4] J. Masuch and M. Delgado-Restituto, "A 190-μW zero-IF GFSK demodulator with a 4-b phase-domain ADC," *IEEE J. Solid-State Circuits*, vol. 47, no. 11, pp. 2796–2806, Nov. 2012.

- [5] Bluetooth Specification, Version 5.0, Volume 6 (Low Energy Controller), BluetoothSIG, Kirkland, WA, USA, Dec. 2016.

- [6] G. Chang et al., "A direct-conversion single-chip radio-modem for Bluetooth," in *IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, vol. 1, Feb. 2002, pp. 88–89.

- [7] L. Seung-Wook et al., "A single-chip 2.4 GHz direct-conversion CMOS transceiver with GFSK modem for Bluetooth application," in Symp. VLSI Circuits. Dig. Tech. Papers, Jun. 2001, pp. 245–246.

- [8] Y.-H. Liu *et al.*, "A 1.9 nJ/b 2.4 GHz multistandard (Bluetooth Low Energy/Zigbee/IEEE802.15.6) transceiver for personal/bodyarea networks," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2013, pp. 446–447.

- [9] M. Contaldo, B. Banerjee, D. Ruffieux, J. Chabloz, E. Le Roux, and C. C. Enz, "A 2.4-GHz BAW-based transceiver for wireless body area networks," *IEEE Trans. Biomed. Circuits Syst.*, vol. 4, no. 6, pp. 391–399, Dec. 2010.

- [10] Y. Liu, R. Lotfi, Y. Hu, and W. A. Serdijn, "A comparative analysis of phase-domain ADC and amplitude-domain IQ ADC," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 3, pp. 671–679, Mar. 2015.

- [11] L. Rajabi, M. Saberi, Y. Liu, A. R. Lotfi, and W. A. Serdijn, "A charge-redistribution phase-domain ADC using an IQ-assisted binarysearch algorithm," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 7, pp. 1696–1705, Jul. 2017.

- [12] Y. Liu, D. Zhao, Y. Li, and W. A. Serdijn, "A 5b 12.9 μW charger distributionphase domain ADC for low power FSK/PSKdemodulation," in *Proc. IEEE Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 275–278.

Xuewei Lei received the B.S. degree in solid state electronics engineering from the University of Electronic Science and Technology of China, Chengdu, China, in 2016. She is currently pursuing the master's degree in electrical and computer engineering with the University of Macau, Macau, China.

Chi-Hang Chan (S'12–M'15) was born in Macau, China, in 1985. He received the B.S. degree in electrical engineering from the University of Washington (U.W. Seattle), Seattle, USA, in 2008, and the M.S. and Ph.D. degrees from the University of Macau, Macau, in 2012 and 2015, respectively. He was an Intern with Chipidea Microelectronics (Now Synopsys), Macau, during his undergraduate studies. He is currently an Assistant Professor with the University of Macau. His research interests include Nyquist analog-to-digital converter (ADC) and mixed signal

circuits. His research mainly focuses on the comparator offset calibration, flash, and multi-bit SAR ADC. He received the Chipidea Microelectronics Prize and the Macau Science and Technology Development Fund (FDCT) Postgraduates Award (Master Level) in 2012 and 2011, respectively. He also received the Macau FDCT Award for Technological Invention (2nd class) and the Macao Scientific and Technological R&D for Postgraduates Award (Ph.D. Level) in 2014 for outstanding academic and research achievements in microelectronics. He was a recipient of the 2015 Solid-State-Circuit-Society (SSCS) Pre-doctoral Achievement Award. He was a co-recipient of the 2011 ISSCC Silk Road Award and the Student Design Contest Award in A-SSCC 2011.

Yan Zhu (S'10–M'12–SM'19) received the B.Sc. degree in electrical engineering and automation from Shanghai University, Shanghai, China, in 2006, and the M.Sc. and Ph.D. degrees in electrical and electronics engineering from the University of Macau, Macau, China, in 2009 and 2011, respectively. She is currently an Associate Professor with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau. She was involved in more than 15 research projects for low-power and high-performance analog-to-digital converter

(ADC). Her research interests include low-power and wideband high-speed Nyquist A/D converters as well as digitally assisted data converter designs. She has published more than 30 technical journals and conference papers in these areas and holds four U.S. patents. She received the Chipidea Microelectronics Prize and the Macao Scientific and Technological R&D for Postgraduates Award (Postgraduate Level) in 2012 for outstanding academic and research achievements in microelectronics and the Student Design Contest Award at the A-SSCC 2011.

**Rui Paulo Martins** (M'88–SM'99–F'08) was born in 1957. He received the bachelor's (five years), the master's, and Ph. D. degrees and the Habilitation for Full Professor in electrical engineering and computers from the Department of Electrical and Computer Engineering, Instituto Superior Técnico (IST), TU of Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

He has been with the Department of Electrical and Computer Engineering (DECE), IST, TU of Lisbon, since 1980. Since 1992, he has been on leave from

IST, TU of Lisbon (University of Lisbon since 2013). He is also with the Department of Electrical and Computer Engineering, Faculty of Science and Technology (FST), University of Macau (UM), Macau, China, where he has been a Chair Professor since 2013. In FST, he was the Dean of the Faculty from 1994 to 1997. He has been the Vice-Rector of UM since 1997. Since 2008, after the reform of the UM Charter, he was nominated after open international recruitment, and reappointed (in 2013), as the Vice-Rector (Research) until 2018. He was a Co-Founder of Chipidea Microelectronics (now Synopsys), Macau, in 2001/2002, and, in 2003, created the Analog and Mixed-Signal VLSI Research Laboratory, UM, elevated in 2011 to the State Key Laboratory of China (the first in engineering in Macau), being its Founding Director. Within the scope of his teaching and research activities, he has taught 21 bachelor's and master's courses and has supervised (or cosupervised) 40 theses, Ph. D. (19) and master's (21). He has coauthored six books and 12 book chapters. He holds 25 Patents: USA (23) and Taiwan (2). He has authored or coauthored 400 papers: in scientific journals (126) and in conference proceedings (274). He has been involved in 62 academic works, in a total of 505 publications.

Dr. Martins was a member of the IEEE CASS Fellow Evaluation Committee from 2013 to 2014. He was a Nominations Committee Member of the IEEE CASS in 2016. In 2010, he was elected, unanimously, as a Corresponding Member of the Portuguese Academy of Sciences, Lisbon, being the only Portuguese Academician living in Asia. He was nominated for the Best Associate Editor of T-CAS II for the period 2012-2013. He was a recipient of two government decorations: The Medal of Professional Merit from Macao Government (Portuguese Administration) in 1999 and the Honorary Title of Value from Macao SAR Government (Chinese Administration) in 2001. He received the IEEE Council on Electronic Design Automation (CEDA) Outstanding Service Award in 2016. He was the General Chair of the 2008 IEEE Asia-Pacific Conference on CAS (APCCAS'2008) and the Vice-President for the Region 10 (Asia, Australia, and the Pacific) of the IEEE CAS Society from 2009 to 2011. He was the General Chair of the ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC'2016). He is also the General Chair of the ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC'2016). He is also the Chair of the IEEE CASS Fellow Evaluation Committee (Class 2018). He was the Founding Chairman of the IEEE Macau Section from 2003 to 2005 and the IEEE Macau Joint-Chapter on Circuits and Systems (CAS)/Communications (COM) from 2005 to 2008 (2009 World Chapter of the Year of IEEE CASS). He was the Vice-President (World) Regional Activities and Membership of the IEEE CAS Society from 2012 to 2013. He was an Associate Editor of the IEEE TRANSACTIONS ON CAS II: EXPRESS BRIEFS from 2010 to 2013. He was the CAS Society Representative in the Nominating Committee, for the election in 2014, of the Division I (CASS/EDS/SSCS), for the Director of the IEEE.