## IEEE ASSCC 2021/ Session 2/ Paper 2.2

## A 95% Peak Efficiency Modified KY (Boost) Converter for IoT with Continuous Flying Capacitor Charging in DCM

Wen-Liang Zeng<sup>1,2</sup>, Caolei Pan<sup>1,3</sup>, Chi-Seng Lam<sup>1</sup>, Sai-Weng Sin<sup>1</sup>, Chenchang Zhan<sup>3</sup>, Rui P. Martins<sup>1,4</sup>

<sup>1</sup>University of Macau, Macao, China

<sup>2</sup>Zhuhai UM Science & Technology Research Institute, Zhuhai, China

<sup>3</sup>Southern University of Science and Technology, Shenzhen, China <sup>4</sup>Universidade de Lisboa, Lisbon, Portugal

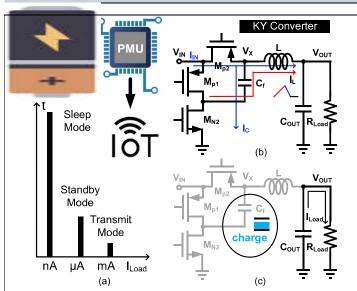

DC-DC converters are required to achieve high efficiency over wide loading range and compact size for IoT applications as shown in Fig. 1(a). However, many designs applied more than one control method to satisfy such requirements [1,2,4,5], which demands complex control system that involves mode selection subsystem, causing efficiency penalty and large chip area. The conventional boost converter has discontinuous output current, which degrades efficiency and output voltage ripple. As a hybrid converter with switched capacitor and inductor, the KY converter overcomes the above drawbacks. However, the charging time of the flying capacitor is seriously limited by the inner operation logic in discontinuous conduction mode (DCM) operation, resulting in small output loading capability and low efficiency.

A modified KY converter is proposed in this work with single control method achieving high efficiency over wide loading range and small silicon area. An additional power switch is inserted in series with the inductor, allowing a better charging of the flying capacitor that is not limited by the DCM period of the proposed converter. The Double-Clock-Time (DCT) control can handle sleep to standby mode, achieving ultra-low quiescent current [1], but not for a full load of hundred mA. We combine DCT control with the power switch adaptive sizing technique to achieve high efficiency and wide output current range (100,000x). A clocked-feedback resistor network (CFRN) is also proposed to further reduce the quiescent current and silicon area. The proposed KY converter is fabricated in a 65nm CMOS, with 0.158 mm², achieving 95% peak efficiency.

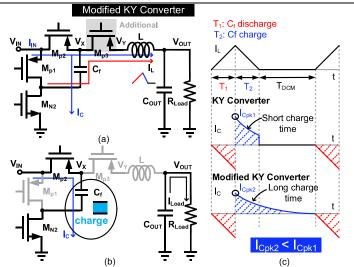

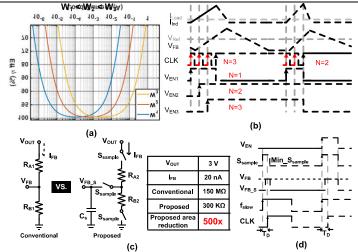

DC-DC converters usually operate in DCM in light-load condition. However, as shown in Fig. 1(b), (c) and Fig. 2(c) in the DCM operation, the flying capacitor Cr charging time of the KY converter is limited by the inductor demagnetization period (T2) and DCM period (T<sub>DCM</sub>), which degrades the output power capability and system stability. Therefore, a modified KY converter overcoming this problem is proposed as shown in Fig. 2(a). An additional power switch  $M_{P3}$  is inserted between node  $V_X$  and the power inductor L. In the T<sub>DCM</sub>, M<sub>P3</sub> turns off, and M<sub>P2</sub> and M<sub>N2</sub> remain on, as shown in Fig. 2(b), so that C<sub>f</sub> charging time is increased from T<sub>2</sub> to T<sub>2</sub>+T<sub>DCM</sub>. Therefore, Cf can be fully charged in the modified KY converter, as shown in Fig. 2(c). The additional MP3 can also simplify the implementation of zero-current-detection (ZCD). In the conventional KY converter, when the reverse current happens, as there are two paths for the I<sub>L</sub> to flow at node V<sub>X</sub>, the conventional ZCD method based on the on-resistance of MP2 cannot detect zero current accurately. With the additional M<sub>P3</sub>, we can simply detect the voltage polarity of MP3 to achieve ZCD and DCM operation precisely. Finally, the peak charging current Icpk2 of the modified KY converter is smaller than the I<sub>Cpk1</sub> of the conventional KY converter, as shown in Fig. 2(c). Therefore, the power loss caused by the Cf charging current is reduced in the proposed KY converter, resulting in enhanced power efficiency.

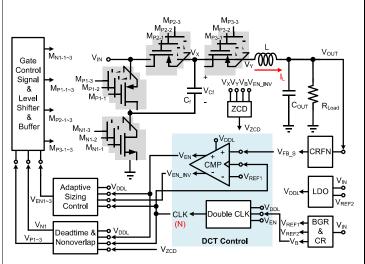

As is shown in Fig. 3, the proposed KY converter system contains a C<sub>f</sub>, an L, an output capacitor C<sub>OUT</sub>, power switches, a CFRN, a low power bandgap and current reference, a low dropout regulator (LDO), a DCT control block, a ZCD control block, an adaptive sizing control block, a non-overlap generator and a gate driver. The DCT control consists of a clocked comparator and double clock generators (a low power slow clock and a fast clock). The clocked comparator compares the sampled output voltage signal V<sub>FB\_S</sub> and V<sub>REF1</sub> at the rising edge of CLK. When V<sub>FB\_S</sub> is smaller than V<sub>REF1</sub>, V<sub>EN</sub> is "high" which turns on the fast clock f<sub>fast</sub> (@ 2.5 MHz). The slow clock (f<sub>slow</sub><300 kHz) determines the switching frequency, and the fast clock determines the on-time (pulse-width) of the power switch

gate signal. One significant advantage of the DCT control is that the fast clock can also be regarded as an indirect current sensor sensing the load current. The fast clock operation times N is proportional to the loading current, which is to be discussed in details next.

Figure 4(a) shows the relationship among efficiency, loading current, and power switch size/width W. When the loading current increases, W should be increased to have high efficiency over a wide loading range. In the DCT control, the number of fast clock action times N is proportional to the loading current. Therefore, in this design, when N=1, only one power switch with size of W<sub>1</sub> is applied; when N=2, two power switches (W<sub>1</sub> and W<sub>2</sub>) are applied; when N=3, three power switches (W<sub>1</sub>, W<sub>2</sub> and W<sub>3</sub>) are applied. After when the V<sub>EN3</sub> signal is triggered on, it will be triggered off if N≤2 in the next switching period, as shown in Fig. 4(b). Notice that this technique does not consume additional static current.

In a power-efficient DC-DC converter, the quiescent current consumed in the feedback resistor network should be low, which leads to a large resistor and chip area. To reduce the resistor size, as shown in Fig. 4(c), (d), a CFRN is proposed. The clock comparator should compare  $V_{FB\_s}$  and  $V_{REF1}$  every rising edge of  $f_{slow}$  to regulate output voltage. When  $V_{FB\_s}$  is larger than  $V_{REF1}$ ,  $V_{EN}$  is "low" and no action happens. Then  $S_{sample}$  should be "high" for a very short time (min\_ $S_{sample}$ ) to reduce current consumption. When  $V_{FB\_s}$  is smaller than  $V_{REF1}$ ,  $V_{EN}$  is "high" and the inductor is magnetized. Then  $S_{sample}$  is "high" as long as  $V_{EN}$ . Notice that a time delay  $T_D$  should be inserted between the clocked comparator signal CLK and  $S_{sample}$ . With this technique, 500x smaller resistor size can be achieved when  $V_{OUT}$  = 3 V and  $I_{FB}$  = 20 nA.

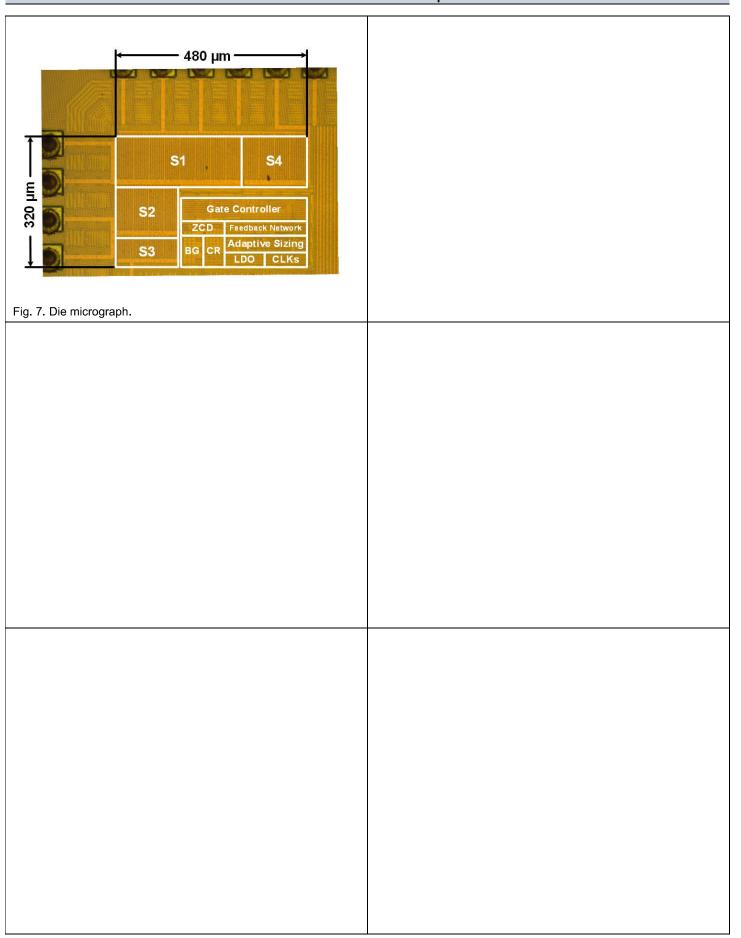

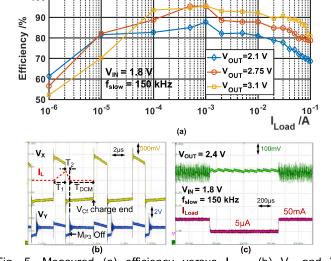

The design is fabricated in a 65 nm CMOS with chip area of 0.158 mm² (0.48 mm x 0.32 mm), as shown in Fig. 7. Fig. 5(a) shows the power efficiency vs.  $I_{\text{Load}}$  at different  $V_{\text{OUT}}$ . With  $f_{\text{slow}}$  = 150 kHz, the efficiency is >80% when  $I_{\text{Load}}$  varies from 30  $\mu\text{A}$  to 100 mA at  $V_{\text{OUT}}$  = 3.1 V. The efficiency is >70% from  $I_{\text{Load}} \ge 10$   $\mu\text{A}$ . The maximum efficiency is 95% when  $I_{\text{Load}}$  is 1 mA and  $V_{\text{OUT}}$  = 2.75V/3.1 V. Fig. 5 (b) shows Vx and Vy waveforms, verifying that the Cr is charging in  $T_{\text{DCM}}$ . Fig. 5 (c) shows the load transient response when  $V_{\text{IN}}$  = 1.8 V,  $V_{\text{OUT}}$  = 2.4 V and  $f_{\text{slow}}$  = 150 kHz, with  $I_{\text{Load}}$  = 5  $\mu\text{A}$  to 50 mA (10,000x). Fig. 6 shows the comparison table with the state-of-the-art DC-DC converters. This work achieves a load range coverage from 1  $\mu\text{A}$  to 100 mA (100,000x), which indicates that the proposed KY DC-DC converter is suitable for IoT applications.

### Acknowledgment:

This work was funded by The Science and Technology Development Fund, Macau SAR (FDCT) (File no. 120/2016/A3, SKL-AMSV(UM)-2020-2022), by the University of Macau (File no. MYRG2018-00020-AMSV, MYRG2020-00056-IME), by the Shenzhen Science and Technology Innovation Commission (SZSTI) under Grants SGDX20201103093601011 and KQJSCX20180319114406851, and by the Zhuhai UM Science & Technology Research Institute (ZUMRI) (File no. CP-015-2020).

#### References:

[1] W.-L. Zeng, Y. Ren, C.-S. Lam, S.-W. Sin, W.-K. Che, R. Ding, R. P. Martins, "A 470-nA Quiescent Current and 92.7%/94.7% Efficiency DCT/PWM Control Buck Converter With Seamless Mode Selection for IoT Application," *IEEE TCAS-I*, vol. 67, no. 11, pp. 4085-4098, Nov. 2020.

[2] S. S. Amin and P. P. Mercier, "MISIMO: A Multi-Input Single-Inductor Multi-Output Energy Harvester Employing Event-Driven MPPT Control to Achieve 89% Peak Efficiency and A 60,000x Dynamic Range in 28nm FDSOI," *ISSCC*, pp.144-146, Feb. 2018. [3] C. Wu, M. Takamiya and T. Sakurai, "Buck Converter with Higher than 87% Efficiency over 500nA to 20mA Load Current Range for IoT Sensor Nodes by Clocked Hysteresis Control," *IEEE CICC*, pp. 1-4, Apr. 2017.

[4] P. Chen, C. Wu and K. Lin, "A 50 nW-to-10 mW Output Power Tri-Mode Digital Buck Converter With Self-Tracking Zero Current Detection for Photovoltaic Energy Harvesting," *IEEE JSSC*, vol. 51, no. 2, pp. 523-532, Feb. 2016.

[5] G. Yu, K. W. R. Chew, Z. C. Sun, H. Tang and L. Siek, "A 400 nW Single-Inductor Dual-Input—Tri-Output DC—DC Buck—Boost Converter With Maximum Power Point Tracking for Indoor Photovoltaic Energy Harvesting," *IEEE JSSC*, vol. 50, no. 11, pp. 2758-2772, Nov. 2015.

# IEEE ASSCC 2021/ Session 2/ Paper 2.2

Fig. 1. (a) Typical IoT device current profile, (b) KY converter topology, and (c) KY converter operates at  $T_{\text{DCM}}$ .

Fig. 2. (a) Proposed modified KY converter topology, (b) modified KY converter operates at  $T_{DCM}$ , and (c)  $I_L$  and  $I_C$  operation waveforms of KY and modified KY converters.

Fig. 3. System block diagram of the proposed KY converter.

Fig. 4. (a) Relationship among efficiency, loading current, and power switch size/width W, (b) DCT control operation waveforms for power switch adaptive sizing technique, (c) proposed CFRN technique, and (d) timing diagram of CFRN.

|      |      | · · ·       | ,    |            |          | <b>\</b> | ,    |         |     |         |

|------|------|-------------|------|------------|----------|----------|------|---------|-----|---------|

| Fig. | 5.   | Measured    | (a)  | efficiency | versus   | Load,    | (b)  | $V_{X}$ | and | $V_{Y}$ |

| wave | efor | ms, and (c) | load | transient  | response | Load     | betw | een     | 5μΑ | and     |

| 50 m | Δ    |             |      |            |          |          |      |         |     |         |

|                                          | This work                  | [1]TCAS-I<br>2020          | [2]ISSCC<br>2018           | [3]CICC<br>2017            | [4]JSSC<br>2016            | [5]JSSC<br>2015             |

|------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|

| Process                                  | 65nm                       | 180nm                      | 28nm                       | 180nm                      | 180nm                      | 180nm                       |

| Topology                                 | KY<br>(Boost)              | Buck                       | Buck-<br>Boost             | Buck                       | Buck                       | Buck<br>-Boost              |

| Control<br>Modes                         | DCT                        | DCT/<br>PWM                | PFM/PWM/<br>SSM            | Clocked<br>Hysteresis      | AM/PFM/<br>PWM             | PSM/<br>PFM                 |

| No. of<br>Modes                          | 1                          | 2                          | 3                          | 1                          | 3                          | 2                           |

| V <sub>IN</sub> (V)                      | 1.5-2.5                    | 2.0-5.0                    | 0.1-1.8                    | 2.4-3.3                    | 0.55-1                     | 1.5-2.5                     |

| V <sub>OUT</sub> (V)                     | 2.1-3.1                    | 0.8-3                      | 0.4-1.4                    | 1.5-1.6                    | 0.35-0.5                   | 1,1.8,3                     |

| L (µH)                                   | 4.7                        | 2.2                        | 10                         | 4.7                        | 4.7                        | 10                          |

| С <sub>оит</sub> /С <sub>f</sub><br>(µF) | 9.4/2                      | 4.7/-                      | 1/-                        | 1/-                        | 4.7/-                      | 10/-                        |

| I <sub>Load</sub><br>(mA)                | 0.001-<br>100              | 0.001-<br>50               | 0.001-<br>60               | 0.0005-<br>10              | 0.0001-<br>20              | 0.001-<br>10                |

| Efficiency<br>(%)                        | 93@<br>10mA<br>70@<br>10µA | 93@<br>10mA<br>86@<br>10µA | 83@<br>10mA<br>76@<br>10µA | 87@<br>10mA<br>88@<br>10µA | 92@<br>10mA<br>79@<br>10µA | 70@<br>10mA<br>82@<br>10 µA |

| Peak_Eff<br>(%)                          | 95@<br>1mA                 | 95@<br>5mA                 | 89@<br>30mA                | 90@<br>1 μA                | 92@<br>10mA                | 83@<br>100µA                |

| Active<br>Area<br>(mm²)                  | 0.158                      | 0.5                        | 0.490                      | 0.71                       | 0.64*                      | 1*                          |

\*: estimated from the paper

Fig. 6. Comparison with the state-of-the-art DC-DC converters.

# IEEE ASSCC 2021/ Session 2/ Paper 2.2