## Auto-Calibration Technique for Current-Based Bandgap Voltage Reference

Chi-Wa U<sup>1</sup>, Man-Kay Law<sup>1</sup>, Chi-Seng Lam<sup>1</sup>, Rui P. Martins<sup>1,2</sup>

<sup>1</sup>University of Macau, Macao, China

<sup>2</sup>Universidade de Lisboa, Lisbon, Portugal

For the industrial application, the bandgap voltage reference (BGR) requires calibration after fabrication to ensure accuracy [1-3] which may lead to expensive labor costs. Some BGRs in the literature were reported without trimming [4,5], however, their output voltages will drift due to device aging and stress [6]. The proposed autocalibration technique can eliminate such a process thus saving costs. Furthermore, the  $\beta$  of the BJT is small in the advance process such that the variation of  $\beta/(\beta+1)$  in V<sub>EB</sub>=(kT/q)*In*[(*I*<sub>E</sub>/*I*<sub>S</sub>)  $\beta/(\beta+1)$ ] has a great influence on V<sub>EB</sub>, resulting in residual temperature coefficient (TC) variation after the conventional one-point trimming. This implies an error in the output, thus reduce stability and lifetime of the system.

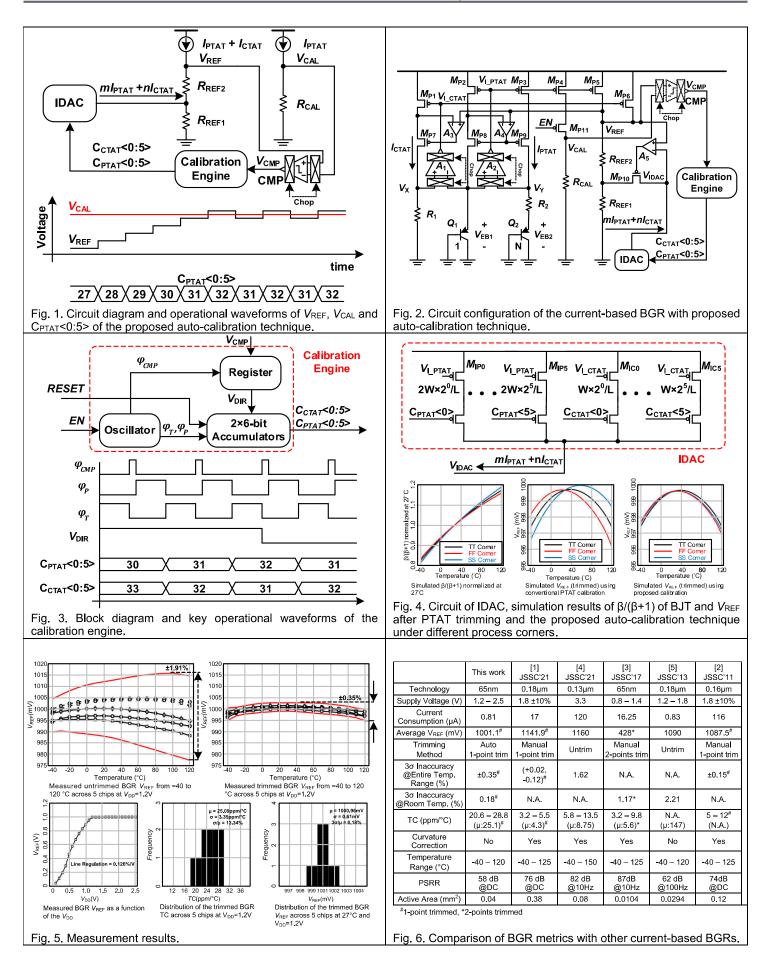

Figure 1 shows the circuit diagram of the proposed auto-calibration technique and its operational waveforms. A conventional currentbased BGR generates the reference ( $V_{\text{REF}}$ ) and the calibrated ( $V_{\text{CAL}}$ ) voltages. We uses a chopped comparator (CMP) to compare  $V_{\text{REF}}$  and  $V_{\text{CAL}}$  at room temperature (27°C) that produces the output  $V_{\text{CMP}}$  to activate the calibration engine. The calibration engine generates two sets of digital signals ( $C_{\text{CTAT}}$ <0:5> and  $C_{\text{PTAT}}$ <0:5>) to control the current digital-to-analog converter (IDAC) and produces the output current  $m_{\text{IPTAT}}$ + $n_{\text{CTAT}}$  employed to bias  $R_{\text{REF1}}$ , so that  $V_{\text{REF}}$  tracks  $V_{\text{CAL}}$  iteratively. As an example, when  $V_{\text{REF}}$ < $V_{\text{CAL}}$ ,  $C_{\text{PTAT}}$ <0:5> increases by one and  $C_{\text{CTAT}}$ <0:5> reduces by one, that is m increases while n decreases, hence  $V_{\text{REF}}$  increases to follow  $V_{\text{CAL}}$ . The calibration engine operates complementarily when  $V_{\text{REF}}$ > $V_{\text{CAL}}$ , and  $V_{\text{REF}}$  converges to  $V_{\text{CAL}}$  after multiple comparison cycles.

Figure 2 presents the circuit configuration of the current-based BGR with proposed auto-calibration technique. Two two-stage chopped amplifiers (A<sub>1</sub> and A<sub>2</sub>) [i.e.,  $V_X = V_Y = V_{EB1}$ ] copy the complementary to absolute temperature (CTAT) voltage  $V_{EB1}$  to the node  $V_X$  and  $V_Y$  in order to generate the CTAT current  $I_{CTAT} = (V_{EB1}/R_1)$  and the proportional to absolute temperature (PTAT) current IPTAT=[(VEB1- $V_{\text{EB2}}/R_2$ ]=(*kT/q*)*In*(*N*)/ $R_2$ . Here, *k* is the Boltzmann constant, *T* is the temperature in Kevin, q is the electron charge and N=8 is the area ratio of Q2 and Q1. We use three basic single-stage differential amplifiers ( $A_3$ ,  $A_4$ , and  $A_5$ ) to control the on-resistances of  $M_{P7}$ ,  $M_{P8}$ ,  $M_{P9}$ , and  $M_{P10}$  such that  $V_{IDAC}$  and the drain voltages of  $M_{P1}$ ,  $M_{P2}$ , and  $M_{P3}$  are equal to  $V_{REF}$ , thus eliminating channel length modulation in the current mirror. The IPTAT, copied by MP4 to bias RCAL allows the determination of  $V_{CAL}=[(kT/q)In(N)](R_{CAL}/R_2)$ . As  $V_{CAL}$  depends on the physical constants and the ratio between resistors, it is insensitive to the process variation. Furthermore, an external enable signal (EN) activates this branch only when calibration is necessary to save power,  $M_{P5}$  and  $M_{P6}$  copy the CTAT and the PTAT current to bias RREF, and the IDAC injects the trimming current mIPTAT and through *M*<sub>P10</sub> to bias *пІ*стат  $R_{\text{Ref1}}$ , thus generating  $V_{\text{REF}} = (mI_{\text{PTAT}} + nI_{\text{CTAT}})R_{\text{REF1}} + (I_{\text{PTAT}} + I_{\text{CTAT}})(R_{\text{REF2}} + R_{\text{REF1}}).$

Figure 3 presents the block diagram and key operational waveforms of the calibration engine. *EN* activates the oscillator that generates three clock signals ( $\varphi_{CMP}$ ,  $\varphi_{T}$ ,  $\varphi_{P}$ ). When  $\varphi_{CMP}$  is high, the register updates  $V_{DIR}$  to  $V_{CMP}$ . When  $\varphi_{P}$  is high, it judges whether  $V_{DIR}$  is high or low to control the two accumulators ( $C_{CTAT}<0.5>$  and  $C_{PTAT}<0.5>$ ) into plus or minus mode. The update of  $C_{CTAT}<0.5>$  and  $C_{PTAT}<0.5>$  happens when  $\varphi_{T}$  is high. If the accumulators are in plus mode,  $C_{PTAT}<0.5>$  increases by one and  $C_{CTAT}<0.5>$  reduces by one. If the accumulators are in minus mode,  $C_{PTAT}<0.5>$  reduces by one and  $C_{CTAT}<0.5>$  reduces by one and  $C_{CTAT}<0.5>$  can vary from 0 to 63. Moreover, an external signal (*RESET*) can reset  $C_{PTAT}<0.5>$  to 32 and  $C_{CTAT}<0.5>$  to 31 such that half of the trimming bits are active.

Figure 4 displays the circuit of the IDAC, simulation results of  $\beta/(\beta+1)$  of BJT and  $V_{REF}$  after PTAT trimming and the proposed autocalibration technique under different process corners. Typically, the trimming of the PTAT voltage eliminates process variation [2]. However, as shown in Fig. 4, due to the variation of  $\beta/(\beta+1)$  in  $V_{EB}$ , it is smaller at high temperature and is larger at low temperature in FF corner, and is larger at low temperature and smaller at high temperature in SS corner. After the conventional PTAT trimming, the

VREF,FF becomes smaller at high temperature and larger at low temperature, while the VREESS becomes larger at high temperature and smaller at low temperature. In this case, the first-order TC of  $V_{\text{REF}}$  is large even when we apply a single-point PTAT trimming [3]. To relax this effect, we propose an IDAC where the width of the  $M_{IP0}$ . 5 (current mirror to copy IPTAT) is 2 times larger than the width of MICO-5 (current mirror to copy ICTAT) in this design. For example, in the FF corner, when  $V_{\text{REF}} < V_{\text{CAL}}$ ,  $C_{\text{PTAT}} < 0.5$  increases by one and CPTAT<0:5> decreases by one, they activate two units of *I*PTAT while disable a unit of ICTAT; In SS corner when VREF>VCAL, CPTAT<0:5> decreases by one and  $C_{PTAT}<0:5>$  increases by one, they disable two units of IPTAT while activate a unit of ICTAT. In this case, the VREF.FF becomes larger at high temperature and smaller at low temperature while VREF,SS obtains the opposite results, compared with the conventional trimming of the PTAT voltage. Consequently, we can relax the effect of the variation of  $\beta/(\beta+1)$ .

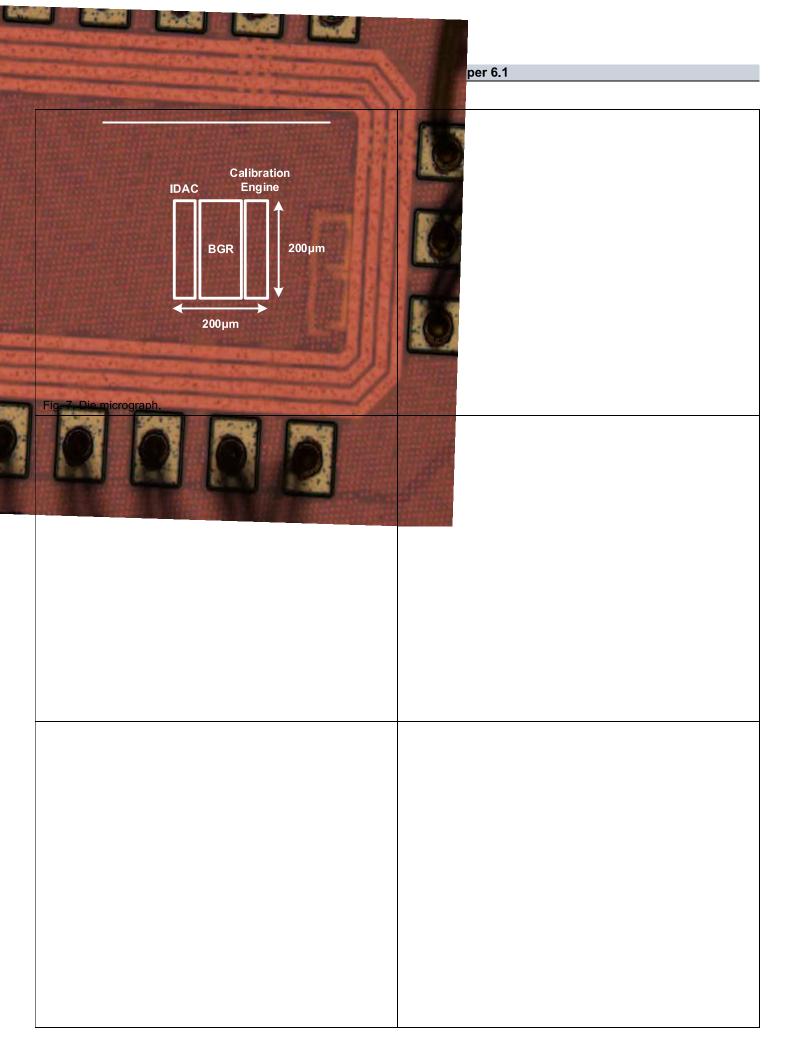

The design is fabricated in a 65nm CMOS process with chip area of 0.04 mm<sup>2</sup> (0.2 mm x 0.2 mm), as shown in Fig. 7. Figure 5 shows the measured V<sub>REF</sub> across temperature (-40°C to 120°C) and V<sub>DD</sub> (1.2V to 2.5V). Before trimming, the V<sub>REF</sub> from -40°C to 120°C for 5 chips varies from 988.4mV to 1004.7mV, with 3 $\sigma$  inaccuracy ±1.91%. After applying the proposed auto-calibration technique, the V<sub>REF</sub> varies from 996.5mV to 1001.6mV, with 3 $\sigma$  inaccuracy ±0.35%. The TC of the BGR varies from 20.6ppm/°C to 28.8ppm/°C and obtains an average TC value of 25.1ppm/°C. Fig. 5 shows the V<sub>REF</sub> variation at 27°C, demonstrating a standard deviation of 0.61mV, corresponding to a 3 $\sigma$ /µ variation of 0.18%. The reference voltage increases by 1.64mV as the supply voltage increases by 1.3V, showing a line regulation of 0.126%/V. The TC of the BGR achieves a 3 $\sigma$  variation of approximately 13.34% at 1.2V V<sub>DD</sub>. The current consumption of the BGR and IDAC is 810nA while the current consumption of the calibration engine is 1.37µA.

Figure 6 compares this work with the state-of-the-art current based BGRs. Compared to the BGRs with manual 1-point trimming [1], [2], the proposed BGR with auto-calibration technique achieves a comparable  $3\sigma$  inaccuracy while obtains a much smaller current and area consumption. Compared to the BGR with manual 2-points trimming [3], although its TC is smaller, it requires 2-points trimming thus increasing costs inevitably. Also, the proposed BGR achieves a much smaller current consumption and better  $3\sigma$  inaccuracy than [3]. Compared to the BGRs without trimming [4], [5], the proposed BGR obtains a much smaller  $3\sigma$  inaccuracy. Although the TC of [4] is small, we achieve a much smaller Current and area consumption. We also achieve a much smaller TC when compared with [5].

## Acknowledgment:

This work was funded by The Science and Technology Development Fund, Macau SAR (FDCT) (File no. 120/2016/A3, SKL-AMSV(UM)-2020-2022), by the University of Macau (File no. MYRG2018-00020-AMSV, MYRG2020-00056-IME), and by the Shenzhen Science and Technology Innovation Commission (SZSTI) (Grant no. SGDX20201103093601011).

## **References:**

[1] J.-H. Boo *et al.*, "A Single-Trim Switched Capacitor CMOS Bandgap Reference With a 3o Inaccuracy of +0.02%, -0.12% for Battery-Monitoring Applications," *IEEE JSSC*, vol. 56, no. 4, pp. 1197–1206, Apr. 2021.

[2] G. Ge *et al.*, "A Single-Trim CMOS Bandgap Reference with a 3σ Inaccuracy of 0.15% From -40°C to 125°C," *IEEE JSSC*, vol. 46, no. 11, pp. 2693–2701, Nov. 2011.

[3] J. Jiang *et al.*, "A 5.6 ppm/°C temperature coefficient, 87-dBPSRR, sub-1-V voltage reference in 65-nm CMOS exploiting the zero-temperature-coefficient point," *IEEE JSSC*, vol. 52, no. 3, pp. 623–633, Mar. 2017.

[4] K. Chen *et al.*, "A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit with a Shared Offset-Cancellation Method for Internal Amplifiers," *IEEE JSSC*, vol. 56, no. 1, pp. 267–276, Jan. 2021.

[5] Y. Osaki et al., "1.2-V Supply, 100-nW, 1.09-V Bandgap and 0.7-V Supply, 52.5-nW, 0.55-V Subbandgap Reference Circuits for Nanowatt CMOS LSIs," *IEEE JSSC*, vol. 48, no. 6, pp. 1530–1538, 2013.

[6] E. Maricau *et al.*, "Transistor Aging-induced Degradation of Analog Circuits: Impact Analysis and Design Guidelines," *ESSCIRC*, pp. 243–246, Sep. 2011.

978-1-6654A4B50zQy/B2E/\$2010011@B20201UEEErsidade de Macau. D56E1cAstaronSQhidasStateooS2rawits@converenceneterstillorod924p/Busan, Korea